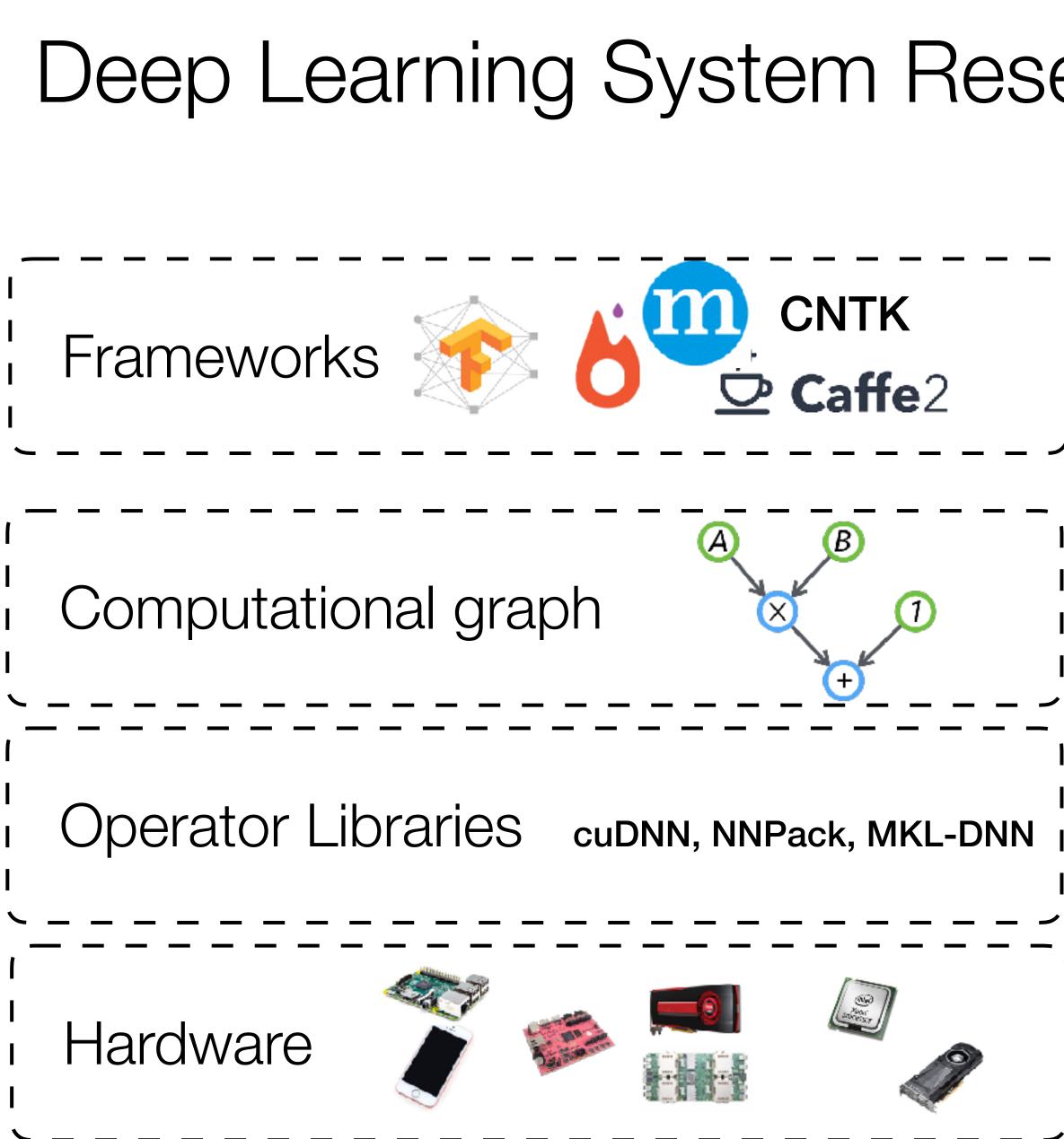

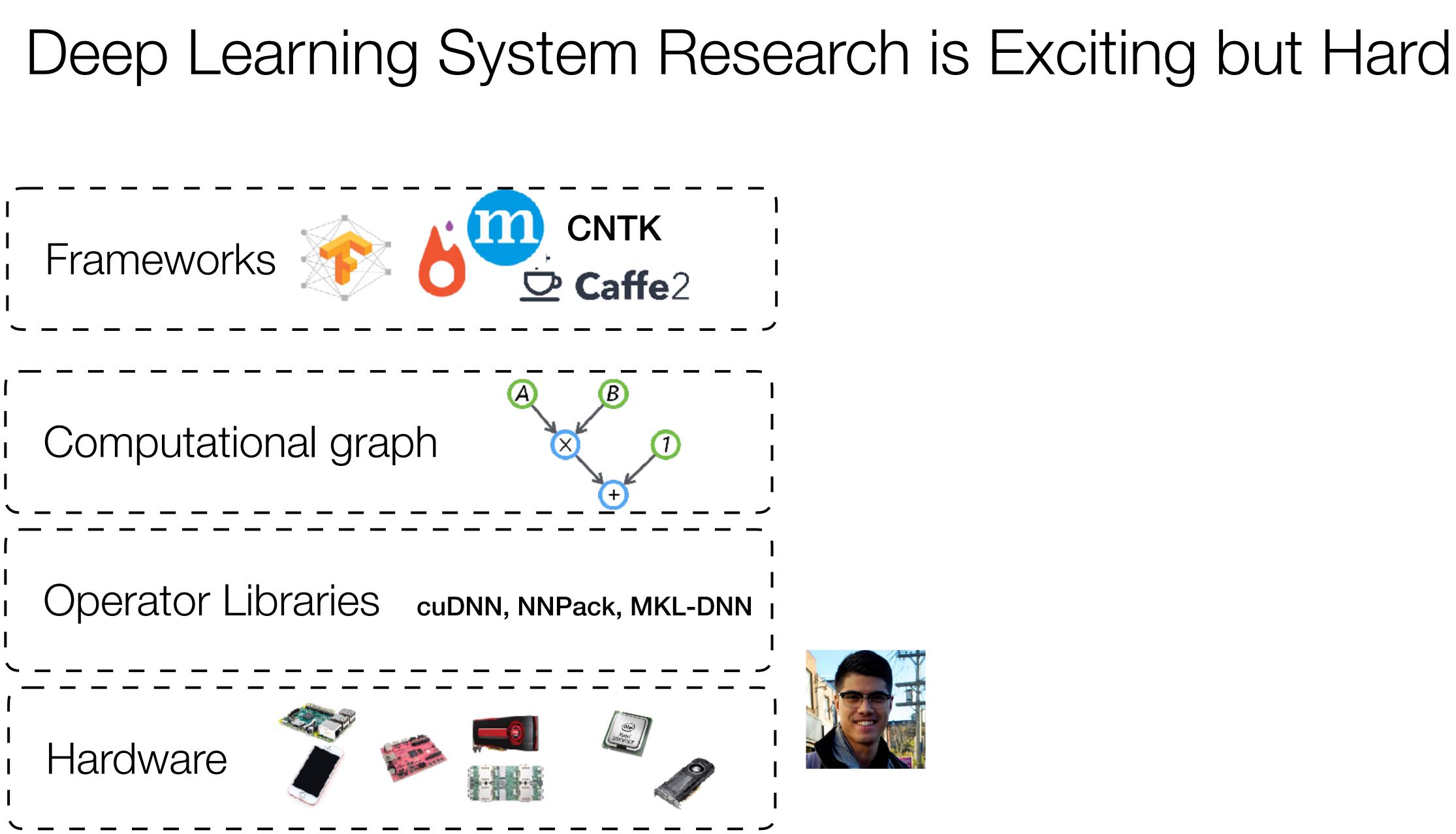

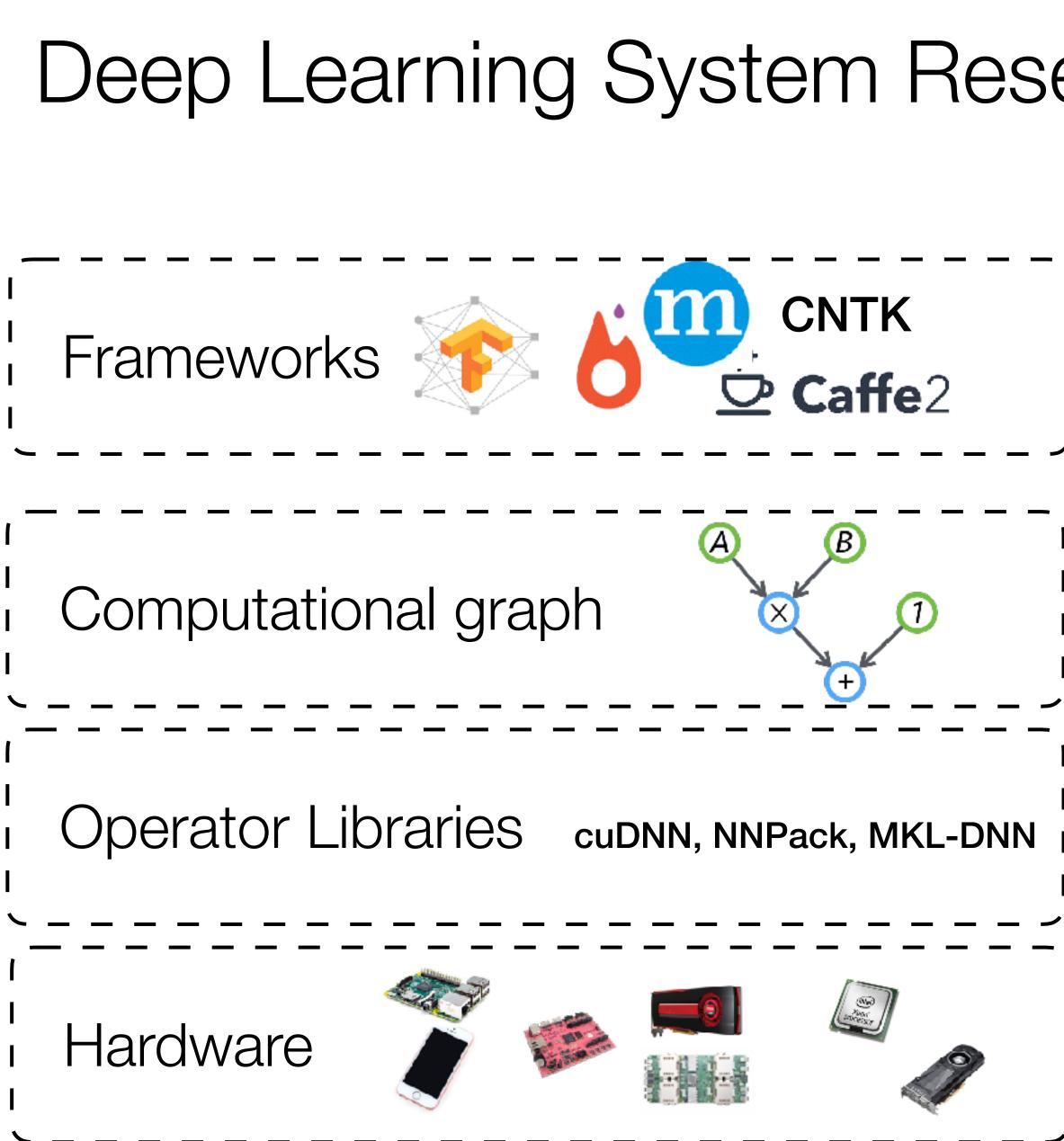

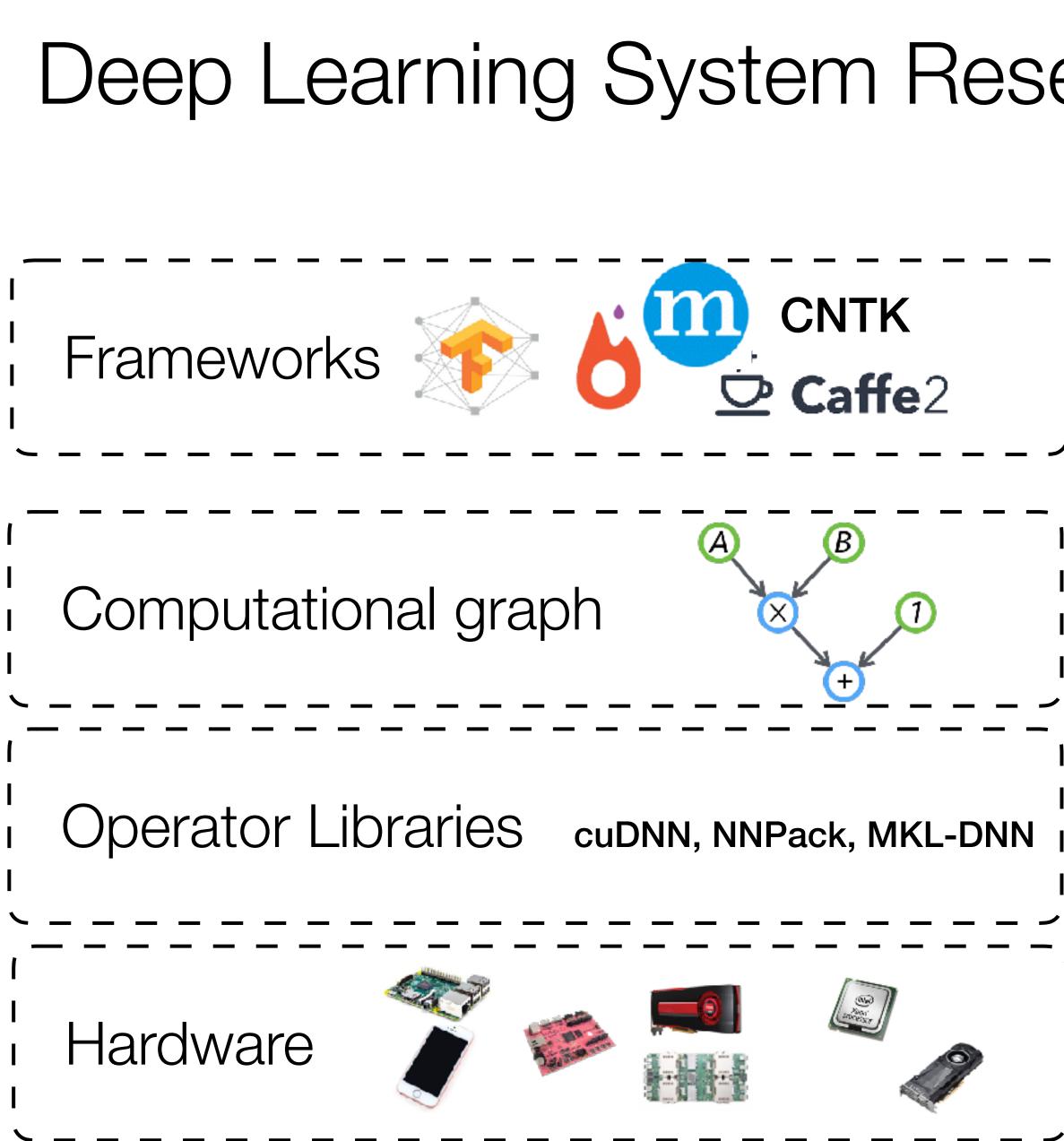

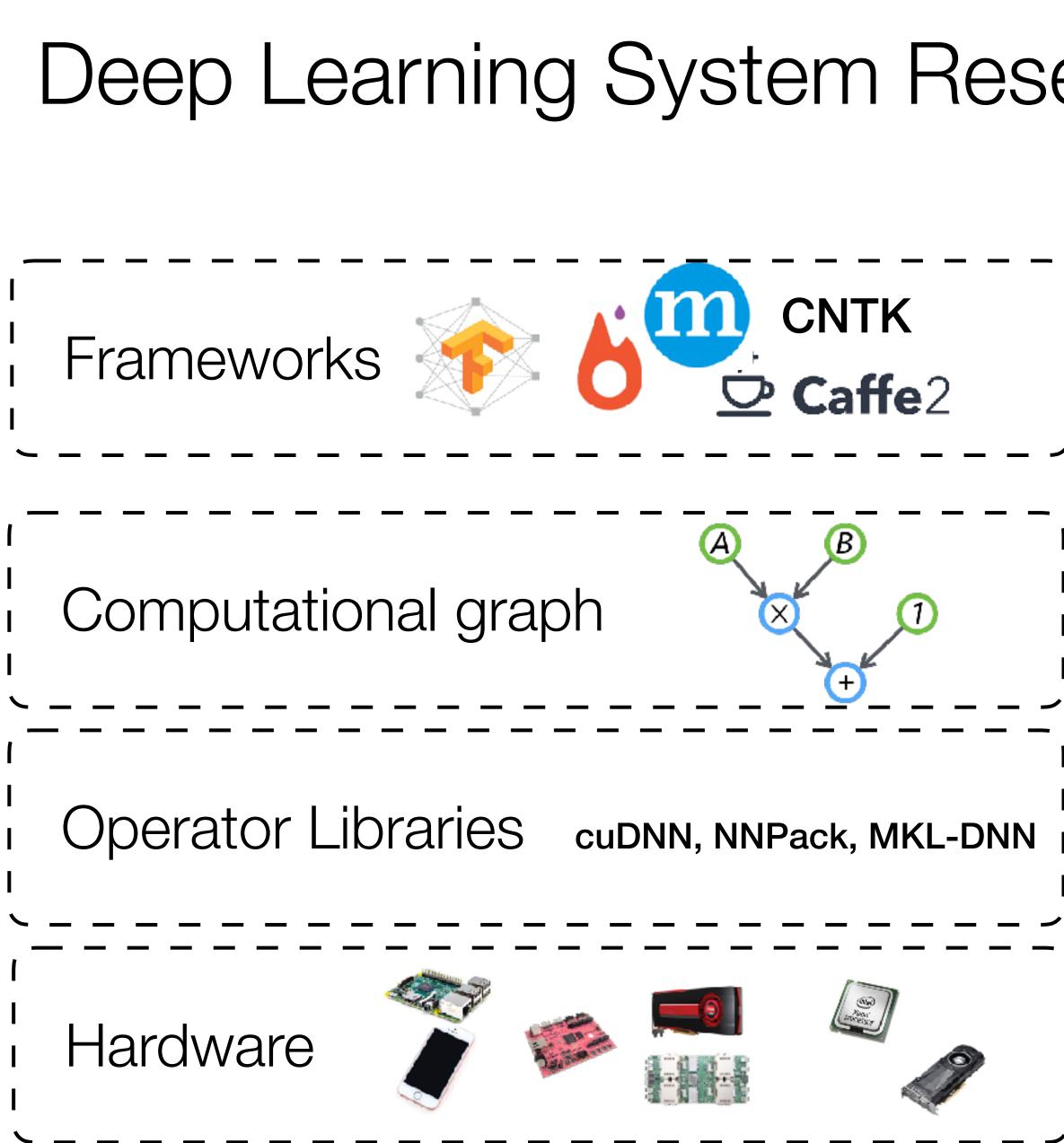

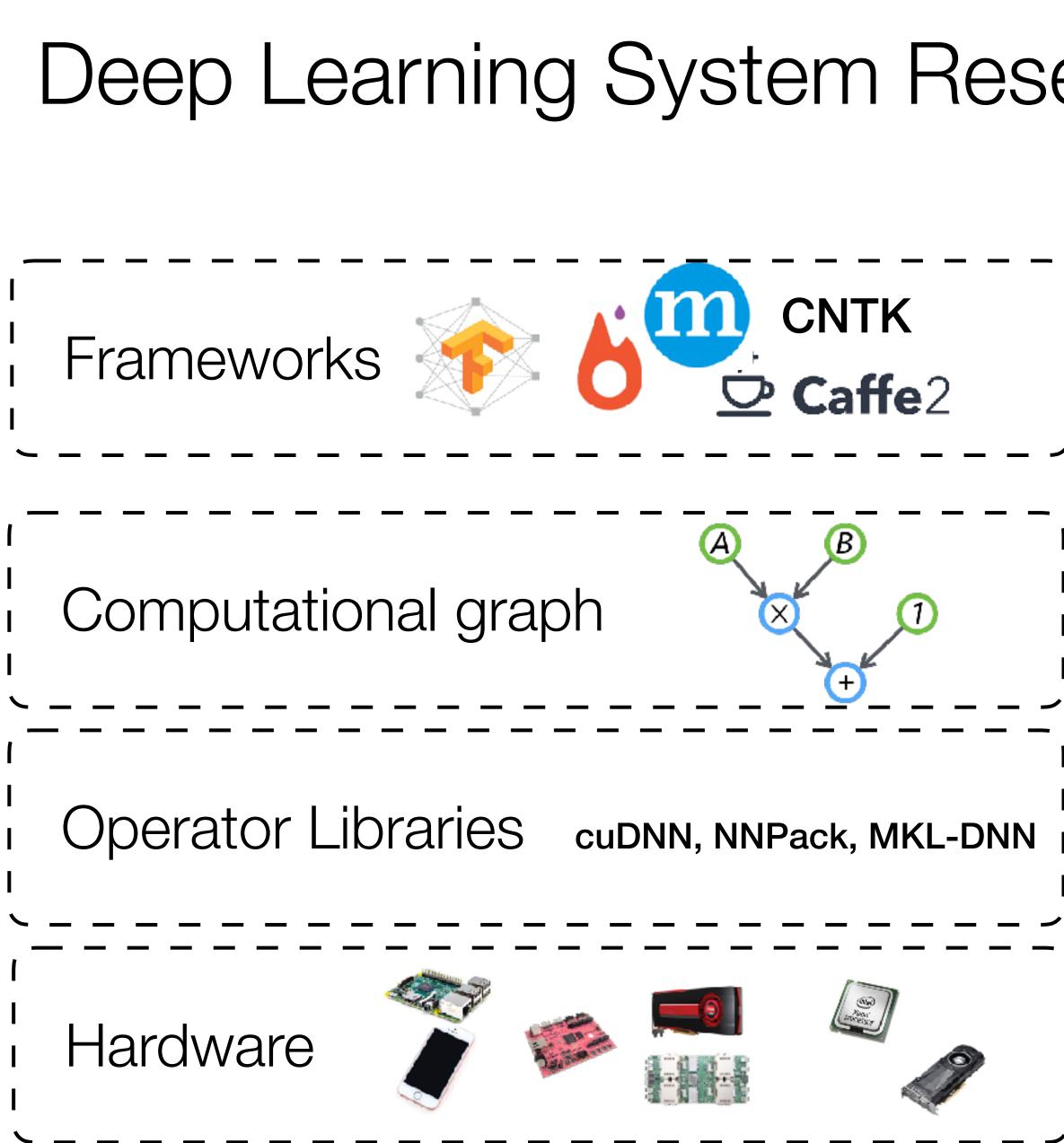

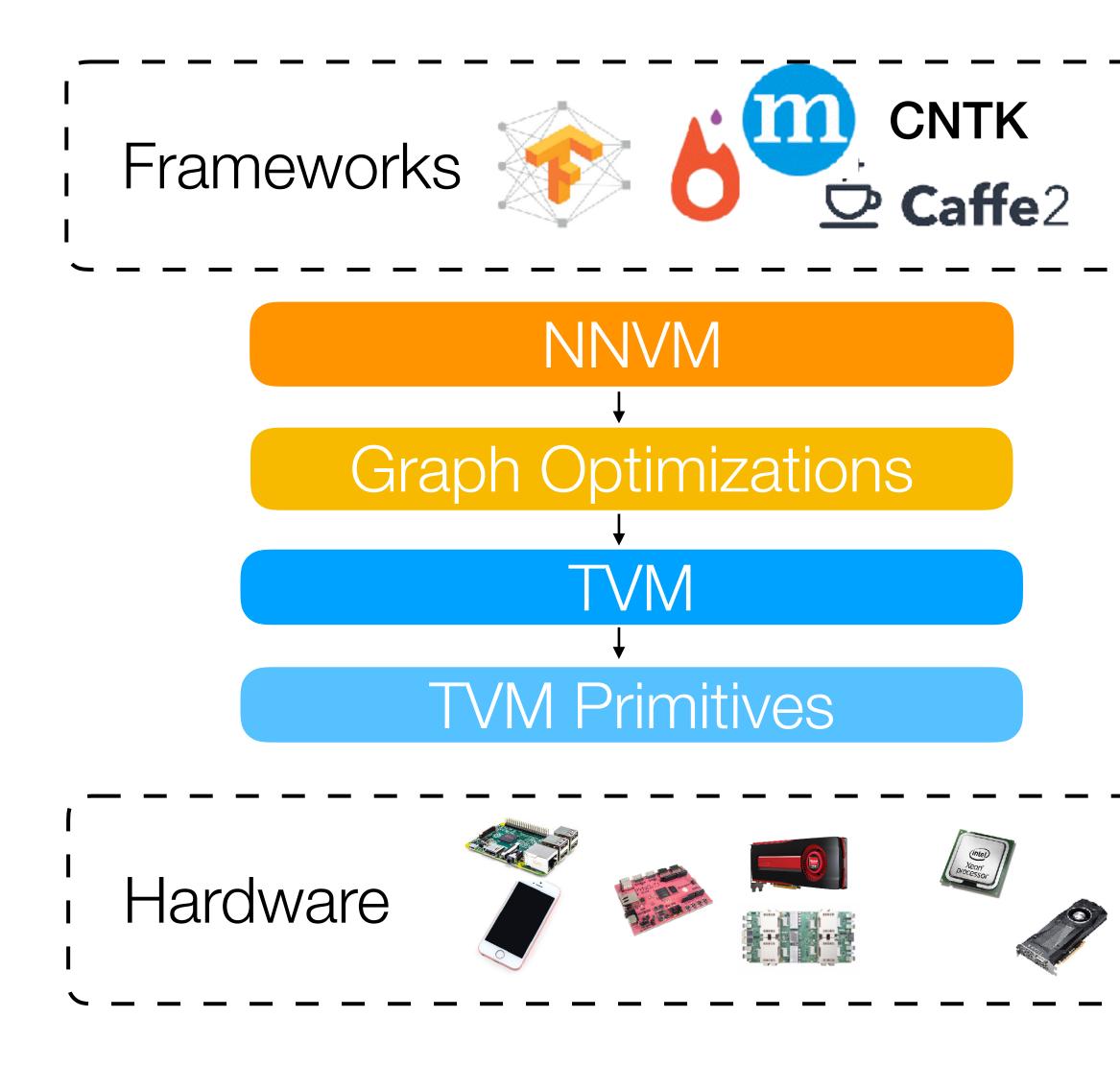

# End to End Optimization Stack for Deep Learning

Presenter: Tianqi Chen

Paul G. Allen School of Computer Science & Engineering University of Washington

# Collaborators

### **University of Washington**

Tianqi Chen

ML, Software Stack

**Thierry Moreau**

Hardware Stack

**Carlos Guestrin**

Luis Ceze

**Arvind Krishnamurthy**

Haichen Shen

GPU

**Ziheng Jiang**

ARM, NNVM pipeline

### and many more contributors in the **DMLC** community

### Built a new accelerator

### Need entire software stack on top of it!

Layout transformation Quantization Operator kernel optimization Benchmarking

. . . .

### Built a new accelerator

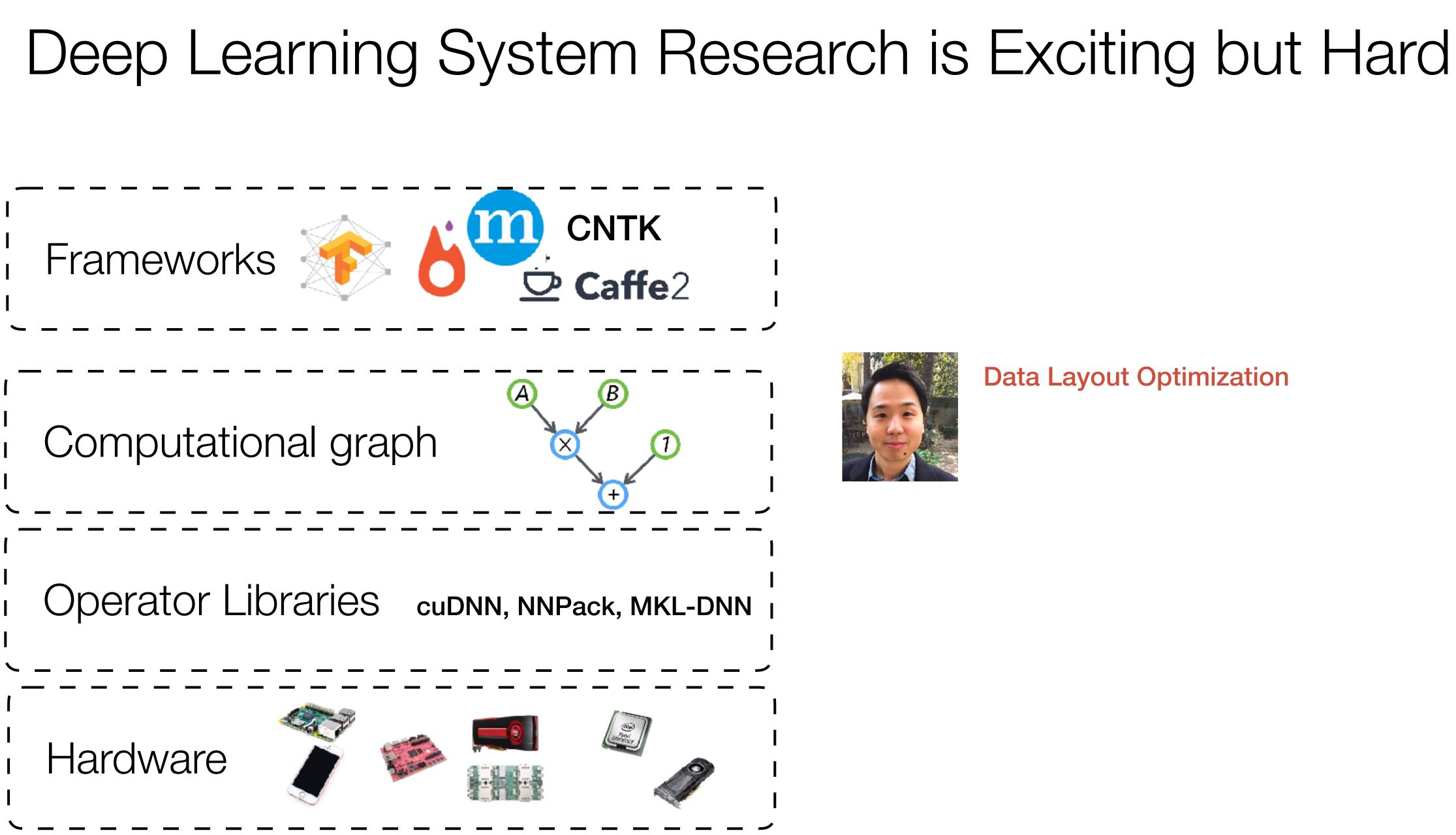

### **Data Layout Optimization**

**Data Layout Optimization Operator Fusion**

**Data Layout Optimization Operator Fusion**

Need optimized hardware kernel for each variant, on each hardware!

**Data Layout Optimization Operator Fusion** Serving

Need optimized hardware kernel for each variant, on each hardware!

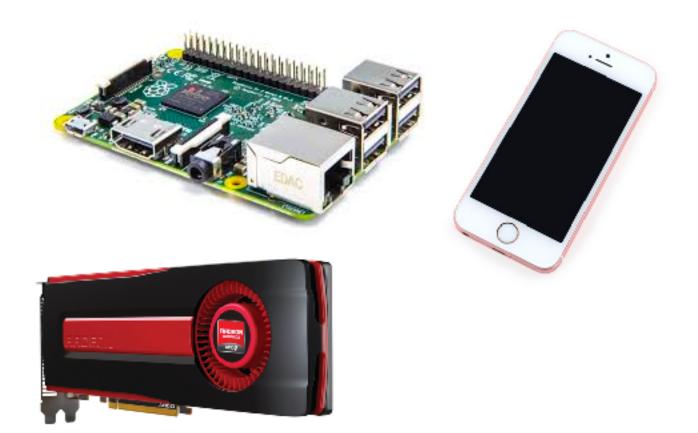

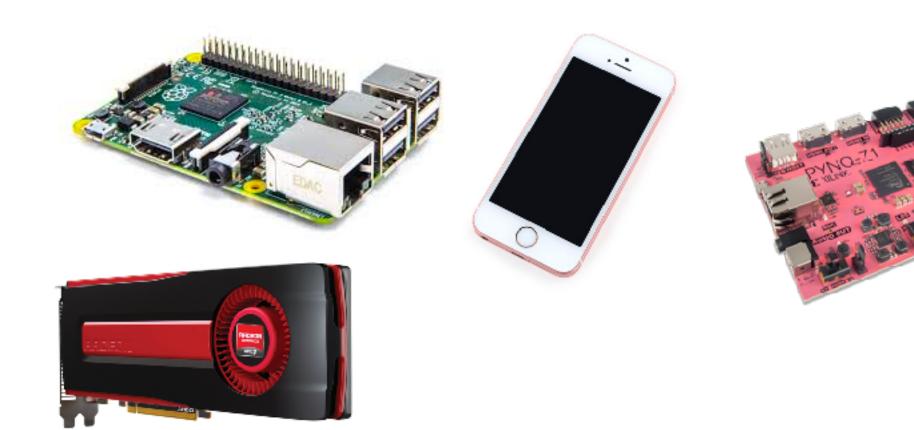

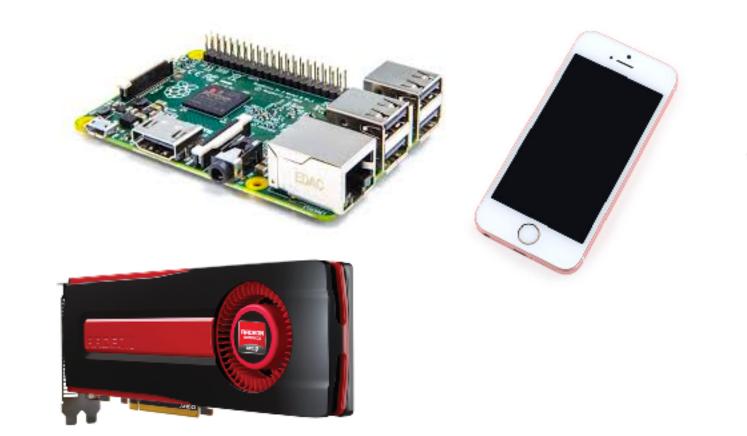

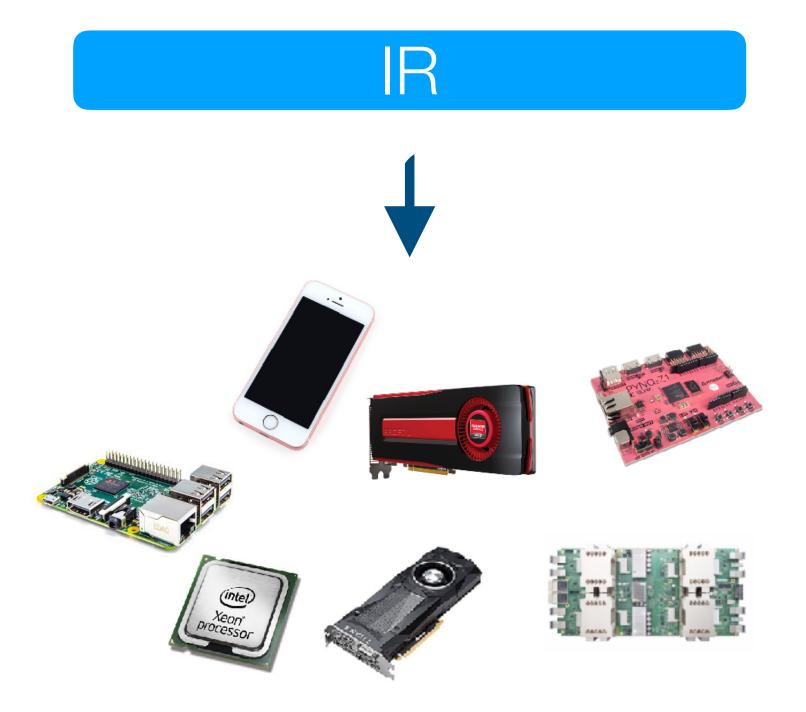

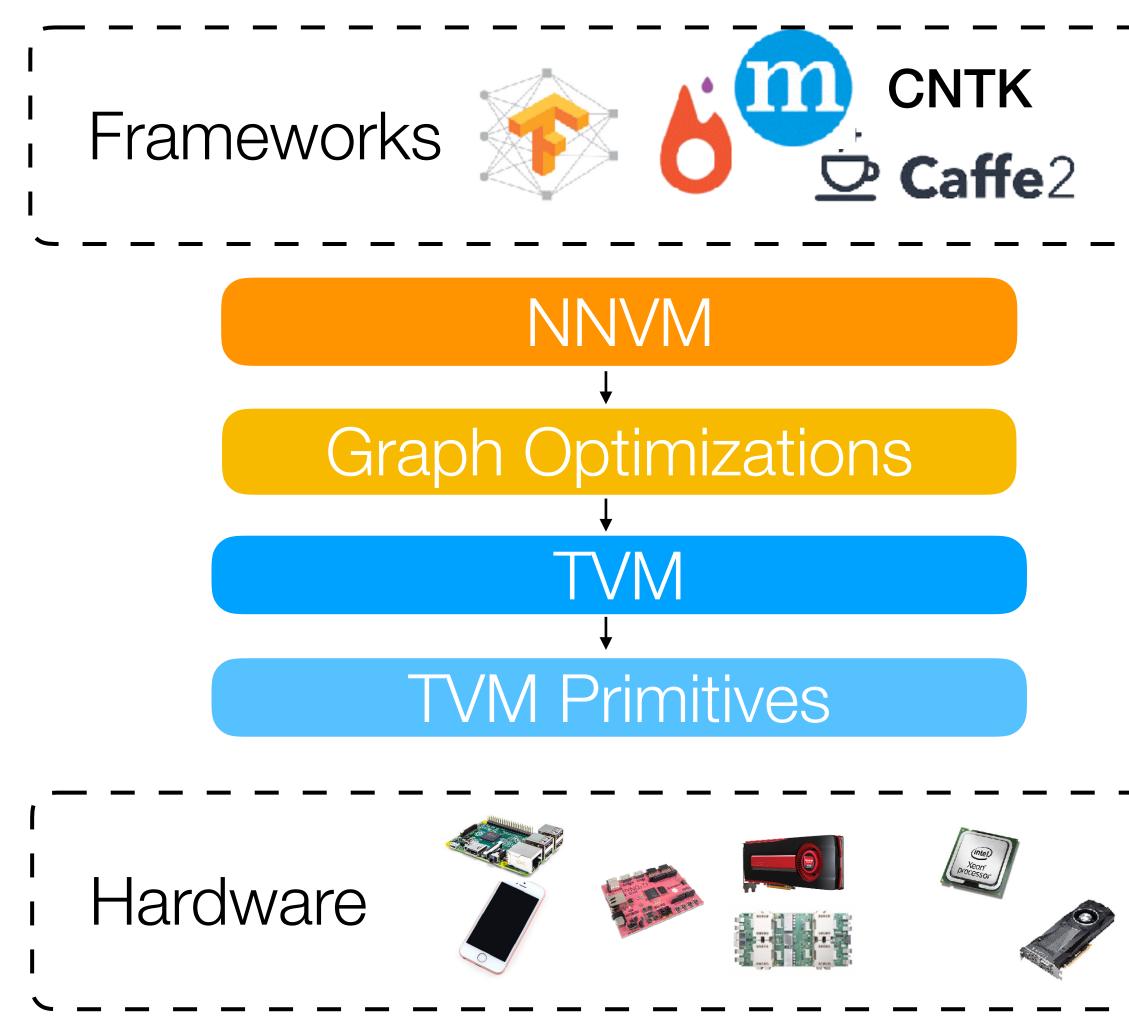

### Hardware Back-Ends

### Intermediate representation

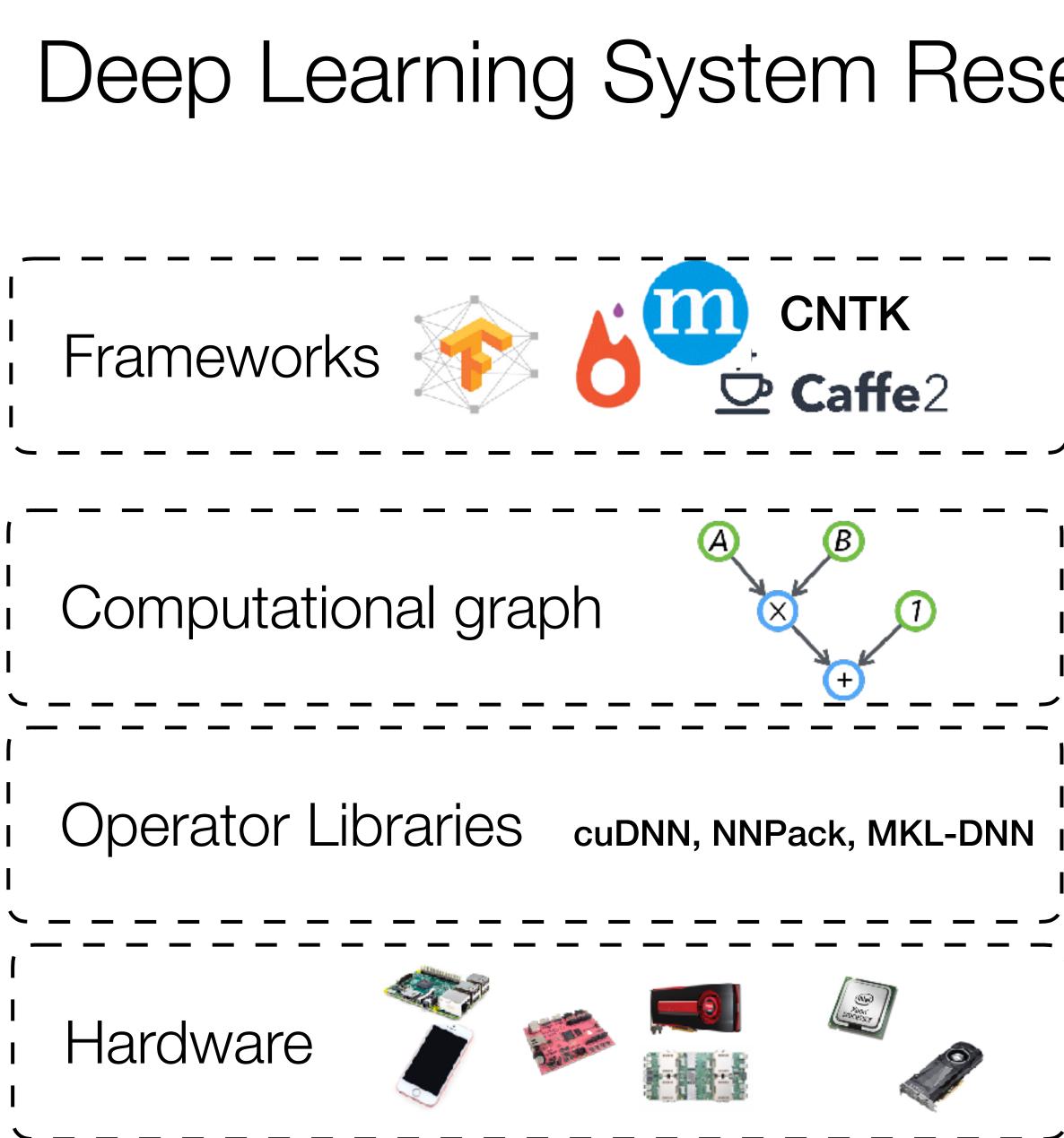

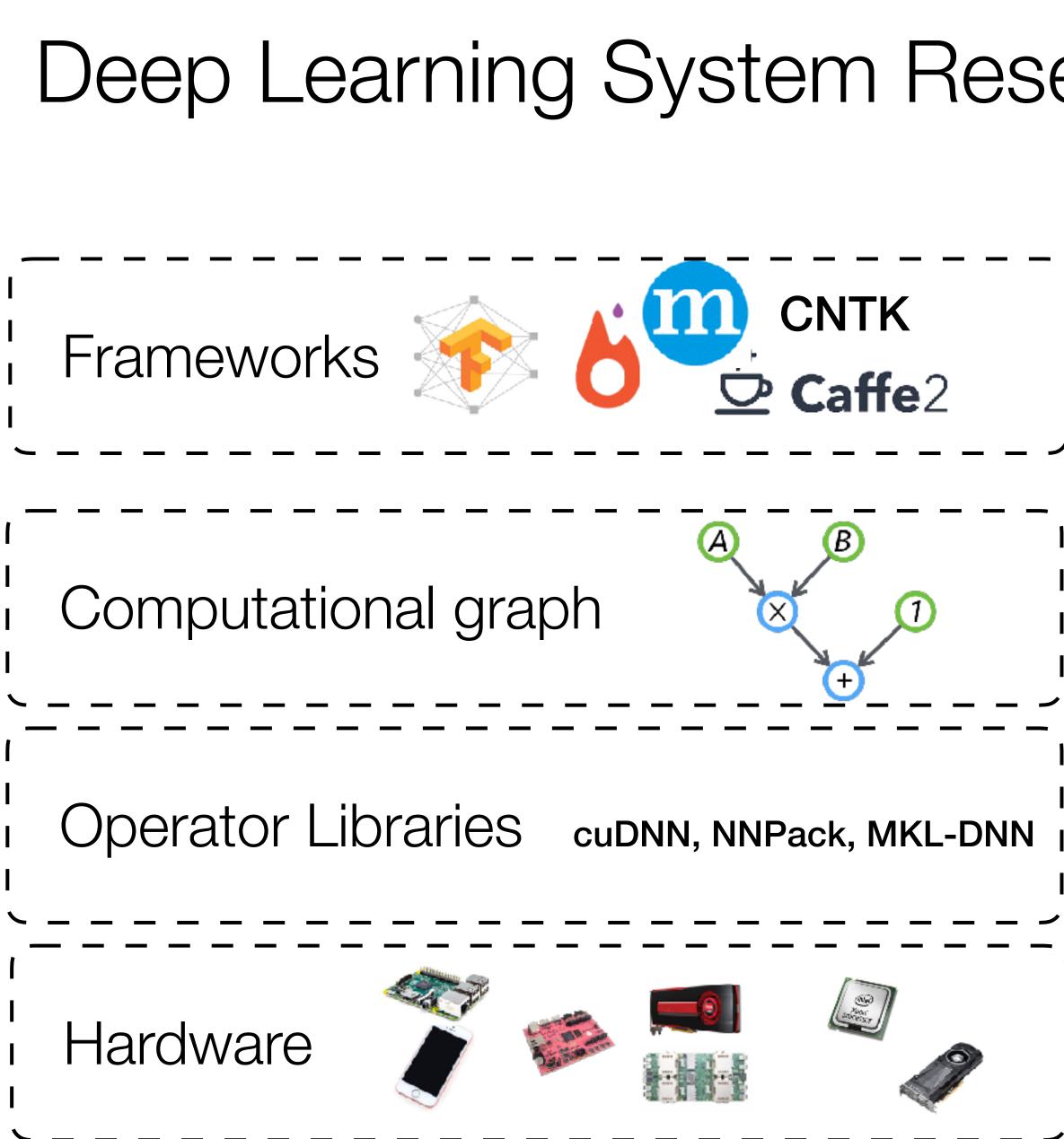

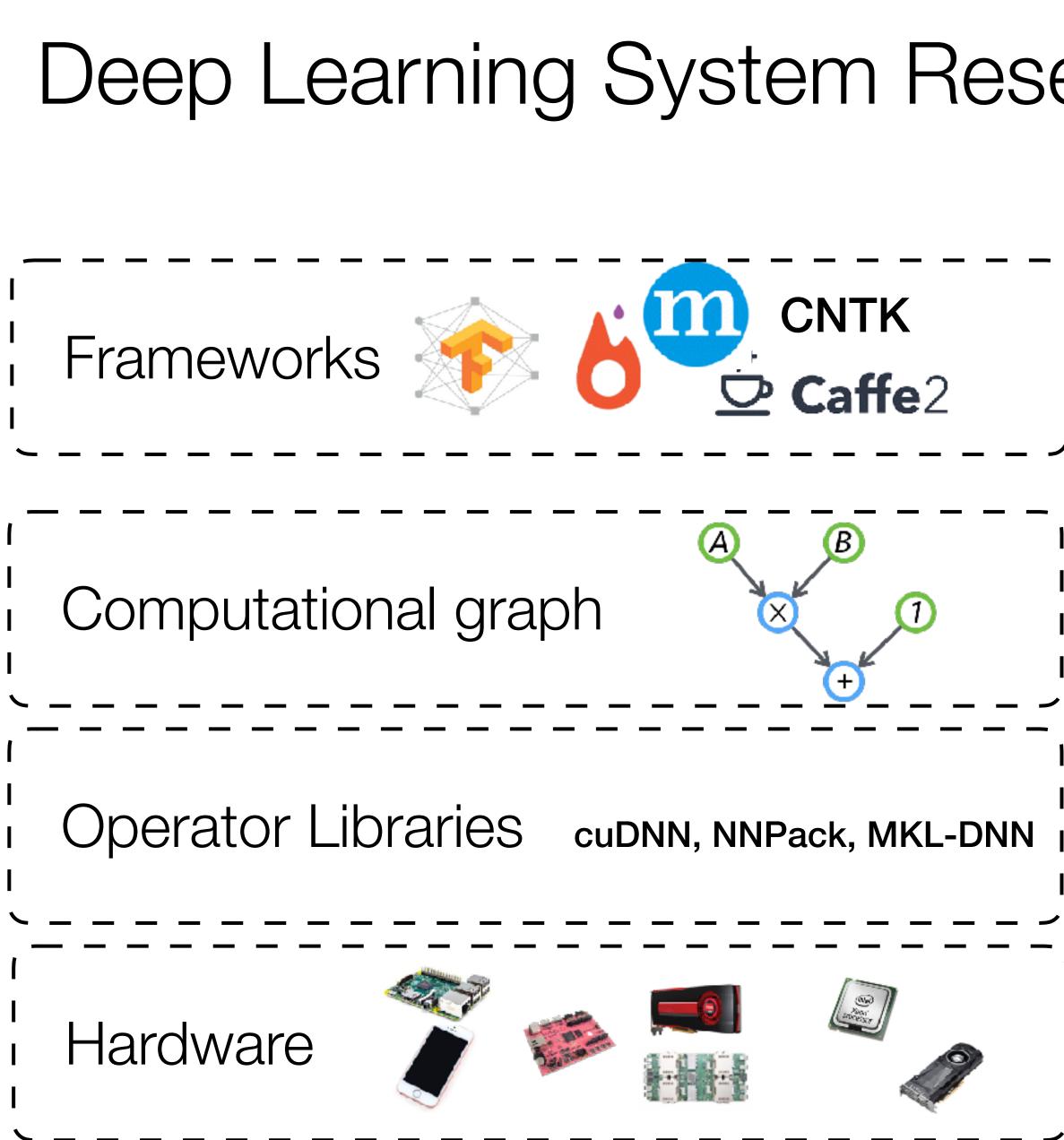

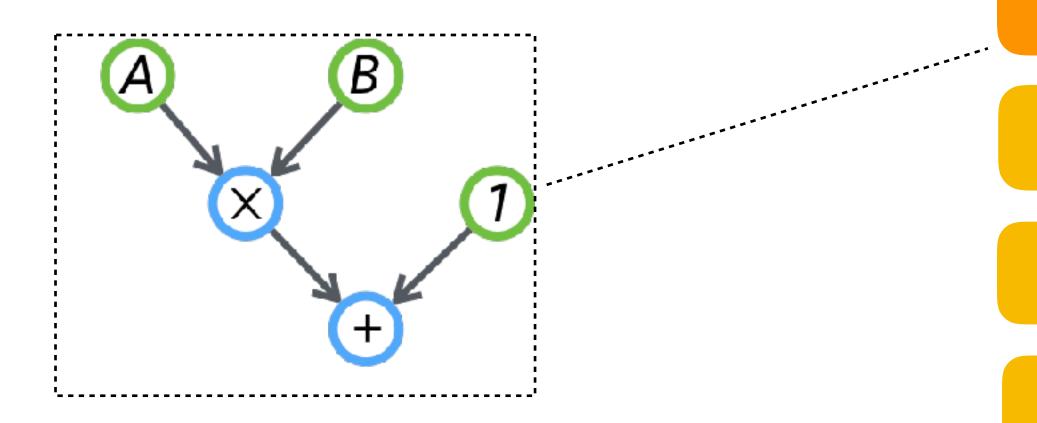

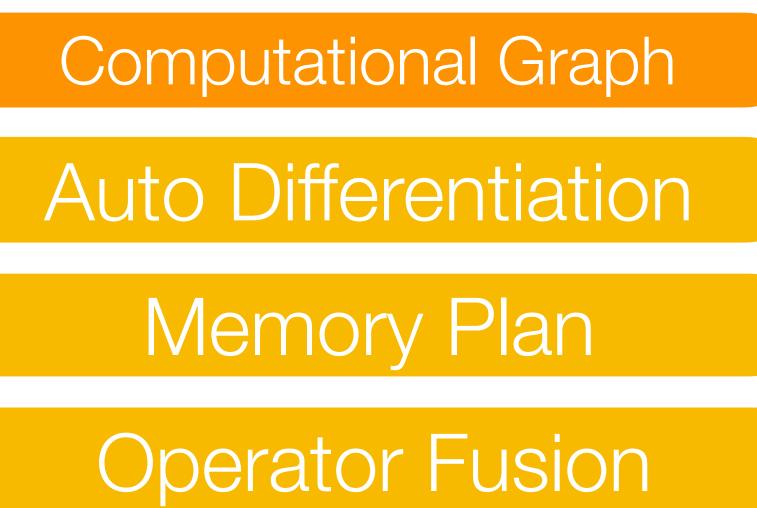

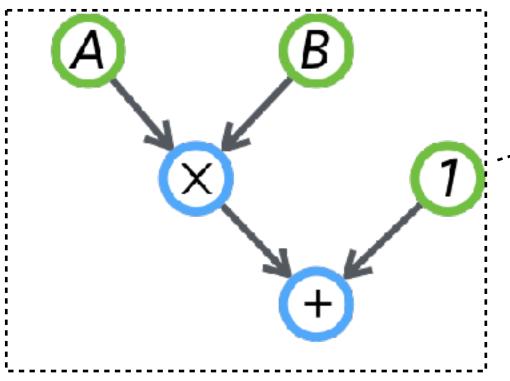

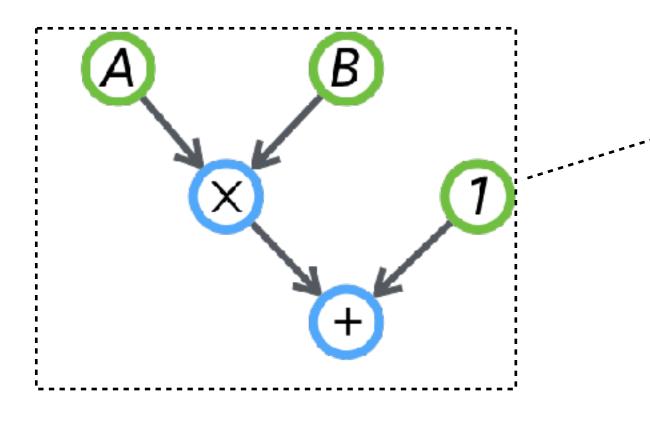

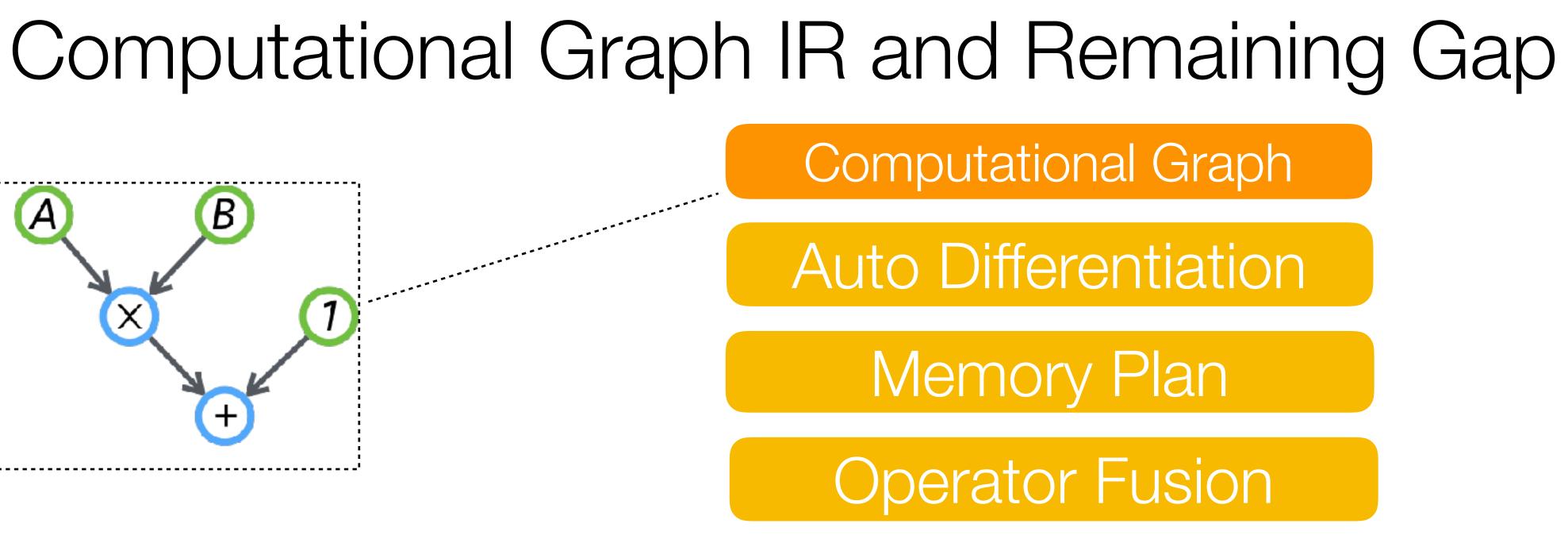

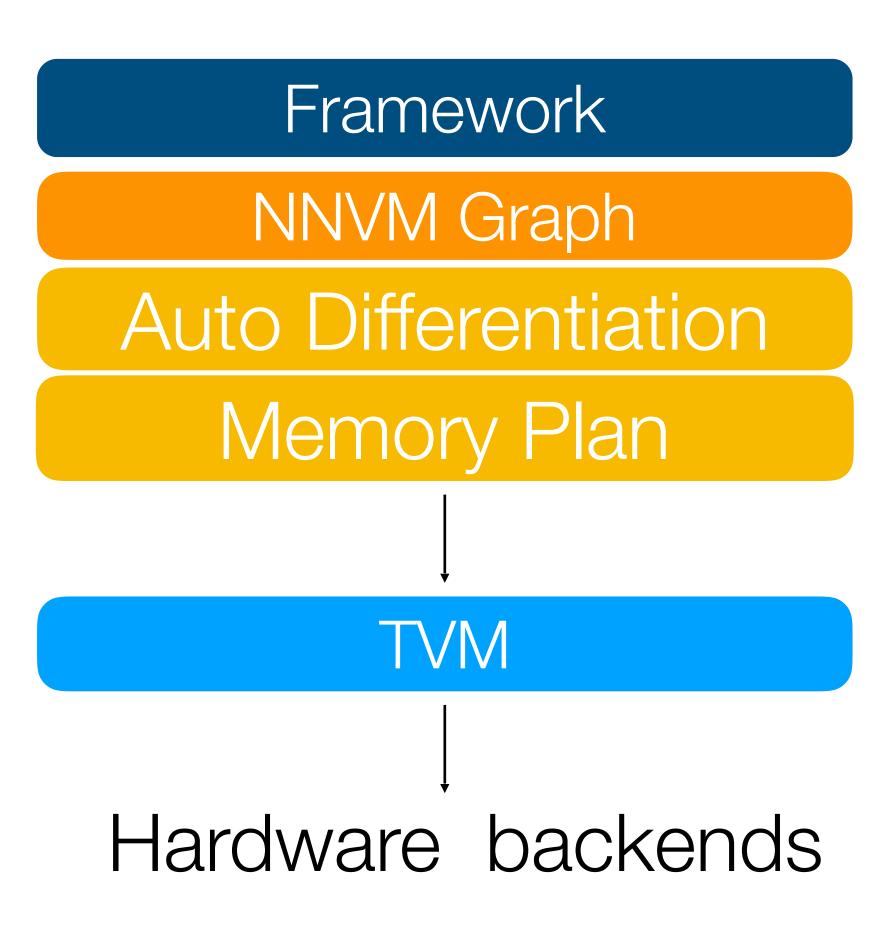

## Computational Graph IR and Remaining Gap

### Examples: NGraph, XLA, NNVM, DLVM ...

### Computational Graph IR and Remaining Gap Computational Graph В A Auto Differentiation Memory Plan

**Operator Fusion**

### too many possible choices: precision, layout, fused pattern, device, threading ... Need a low level IR to express them explicitly

Backends

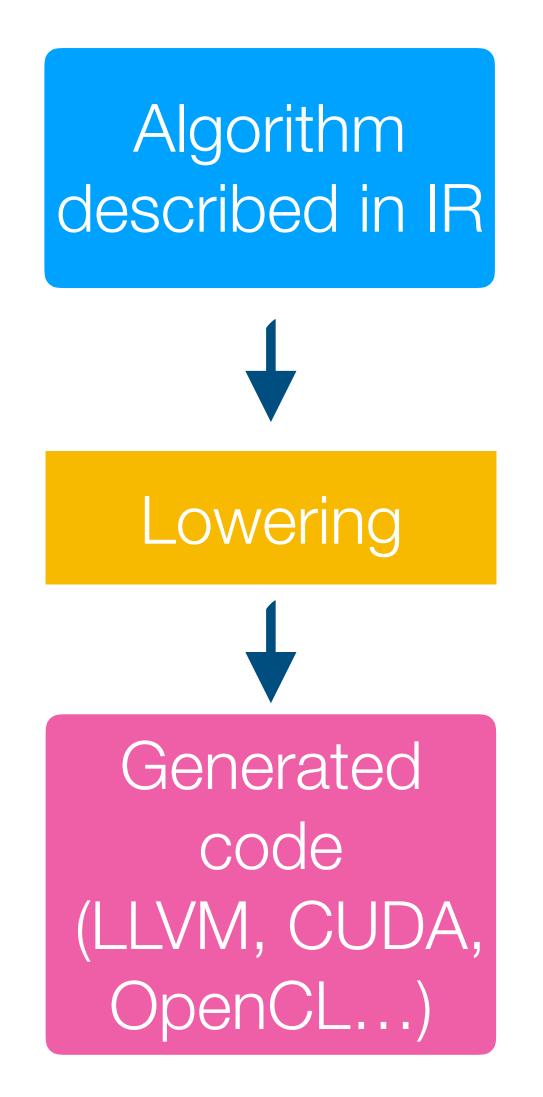

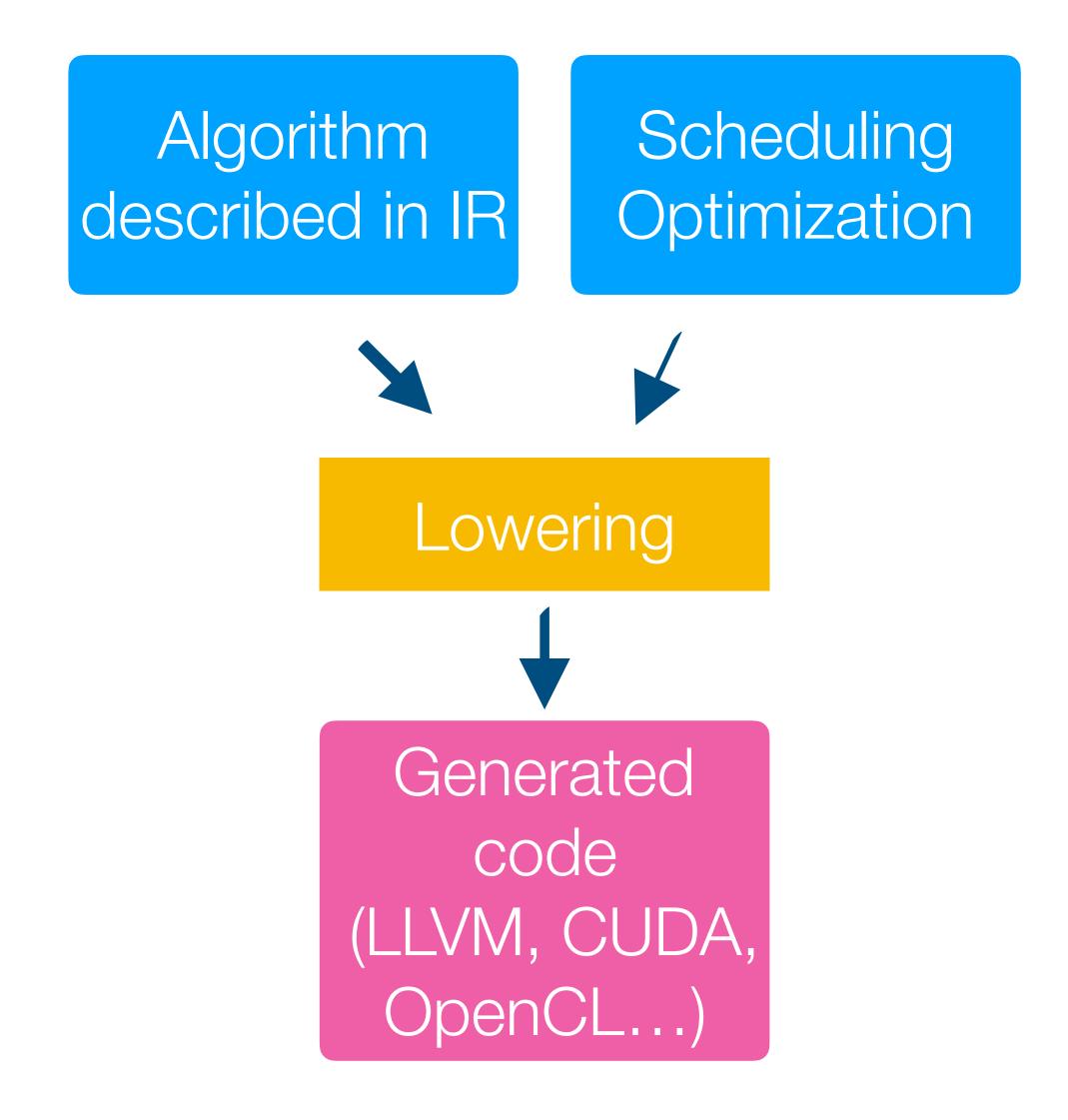

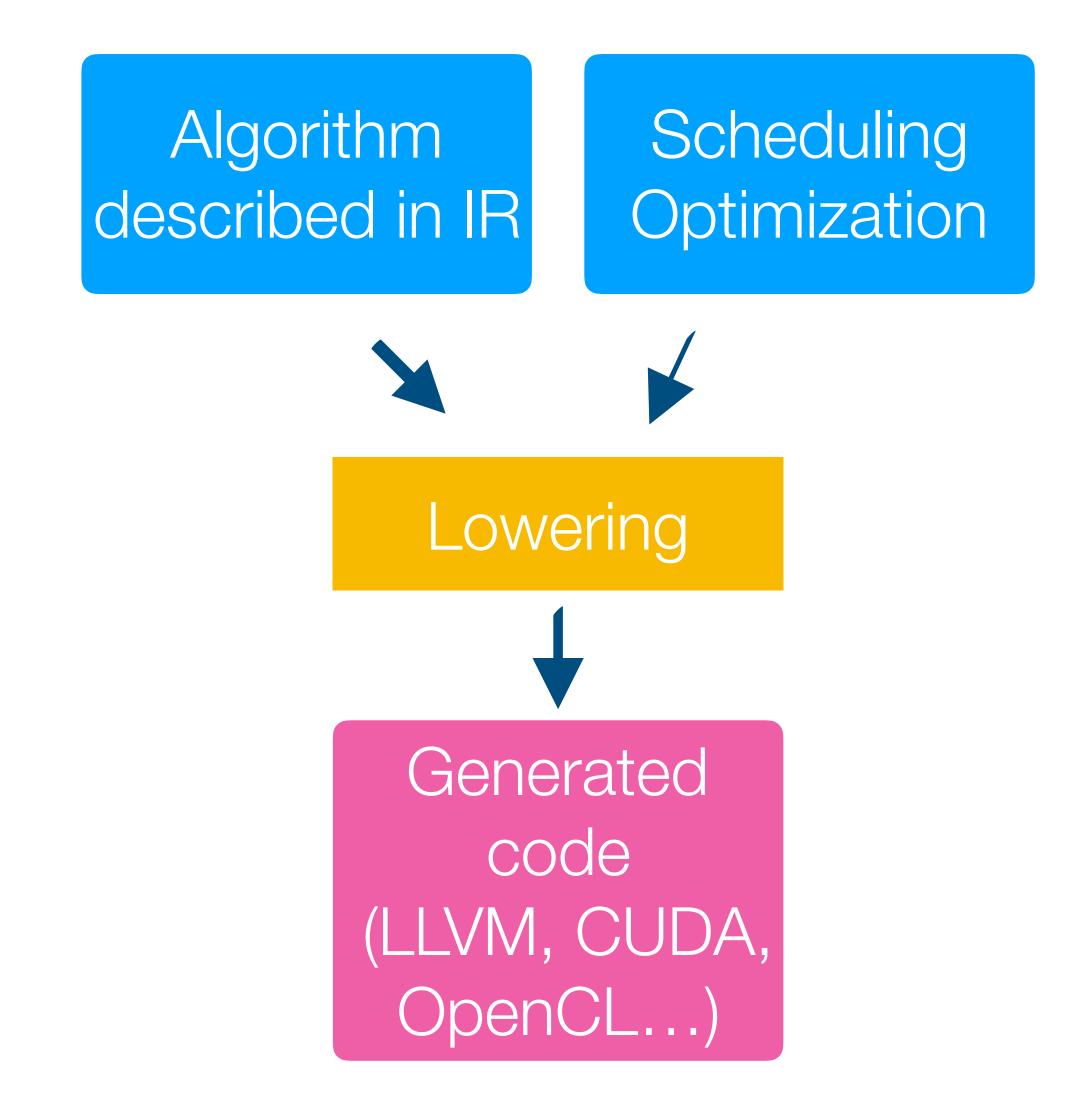

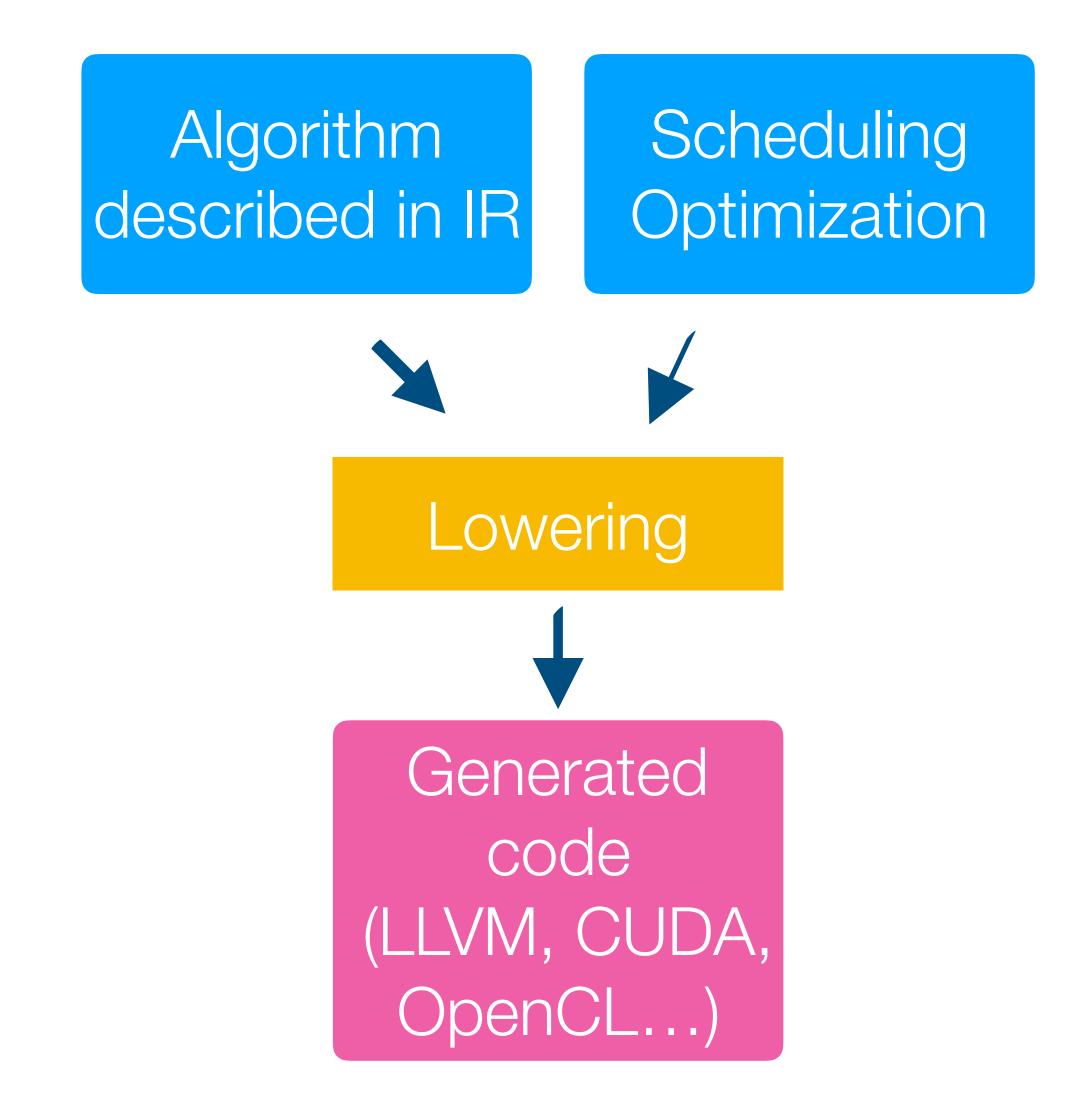

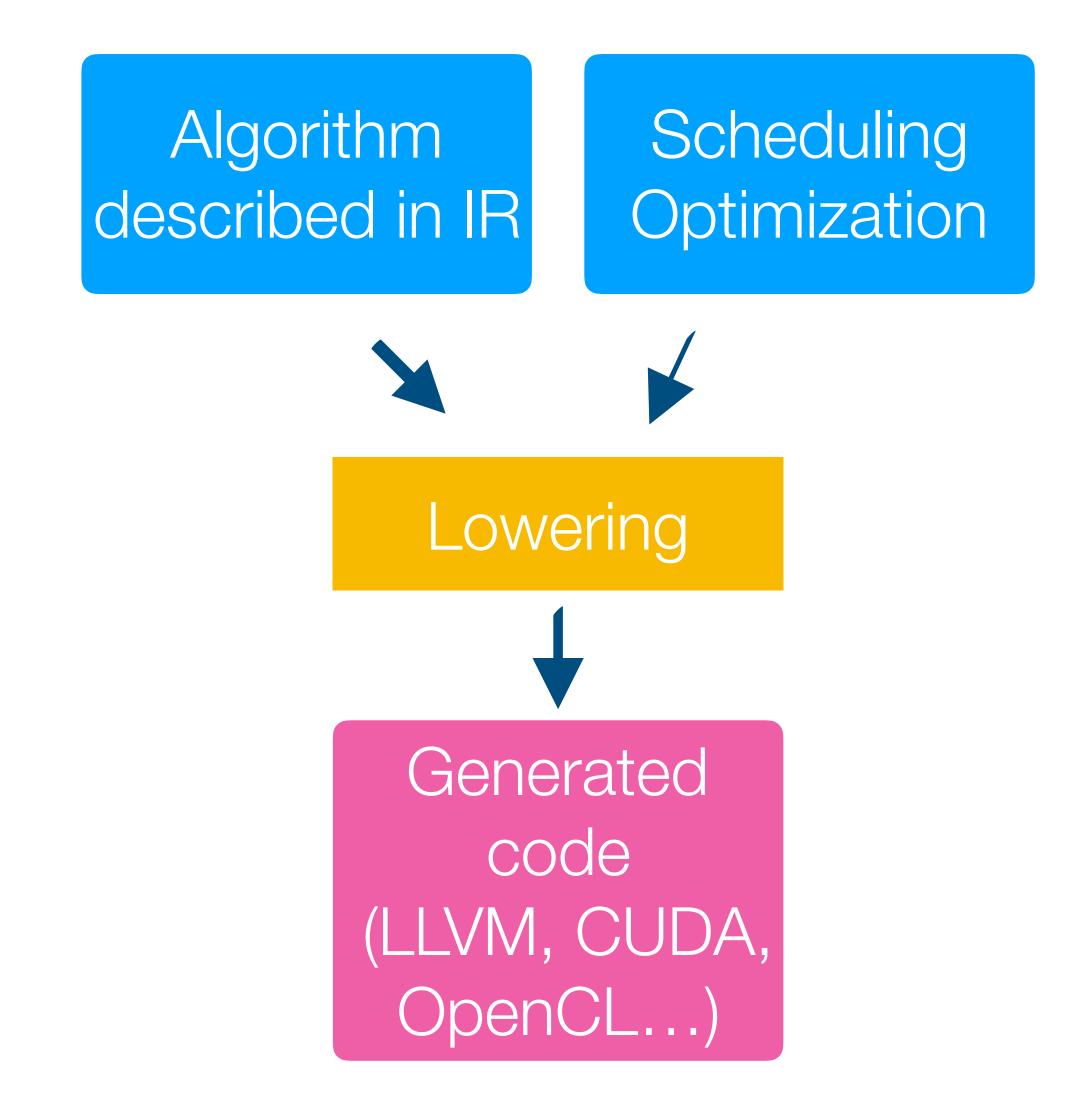

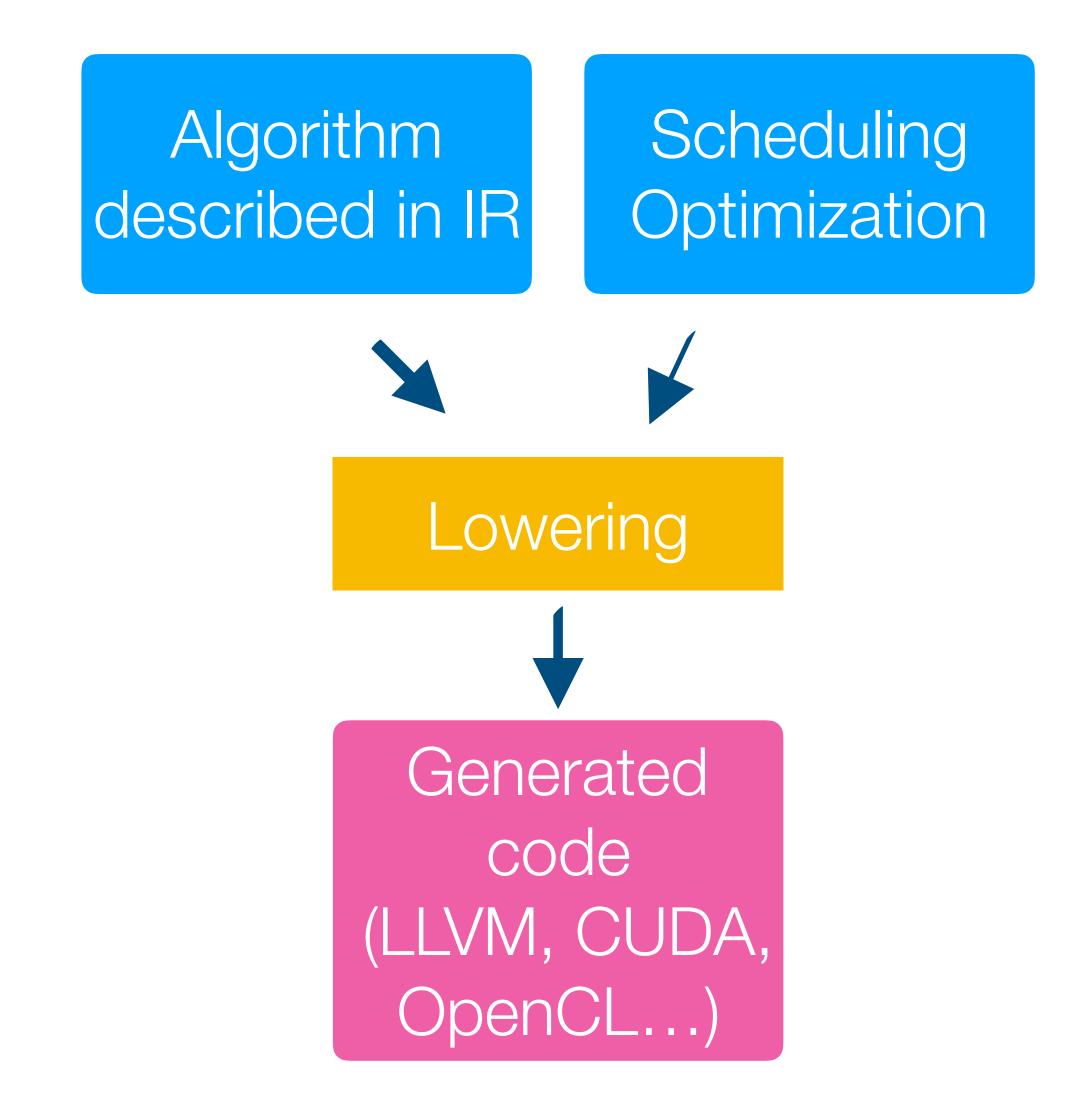

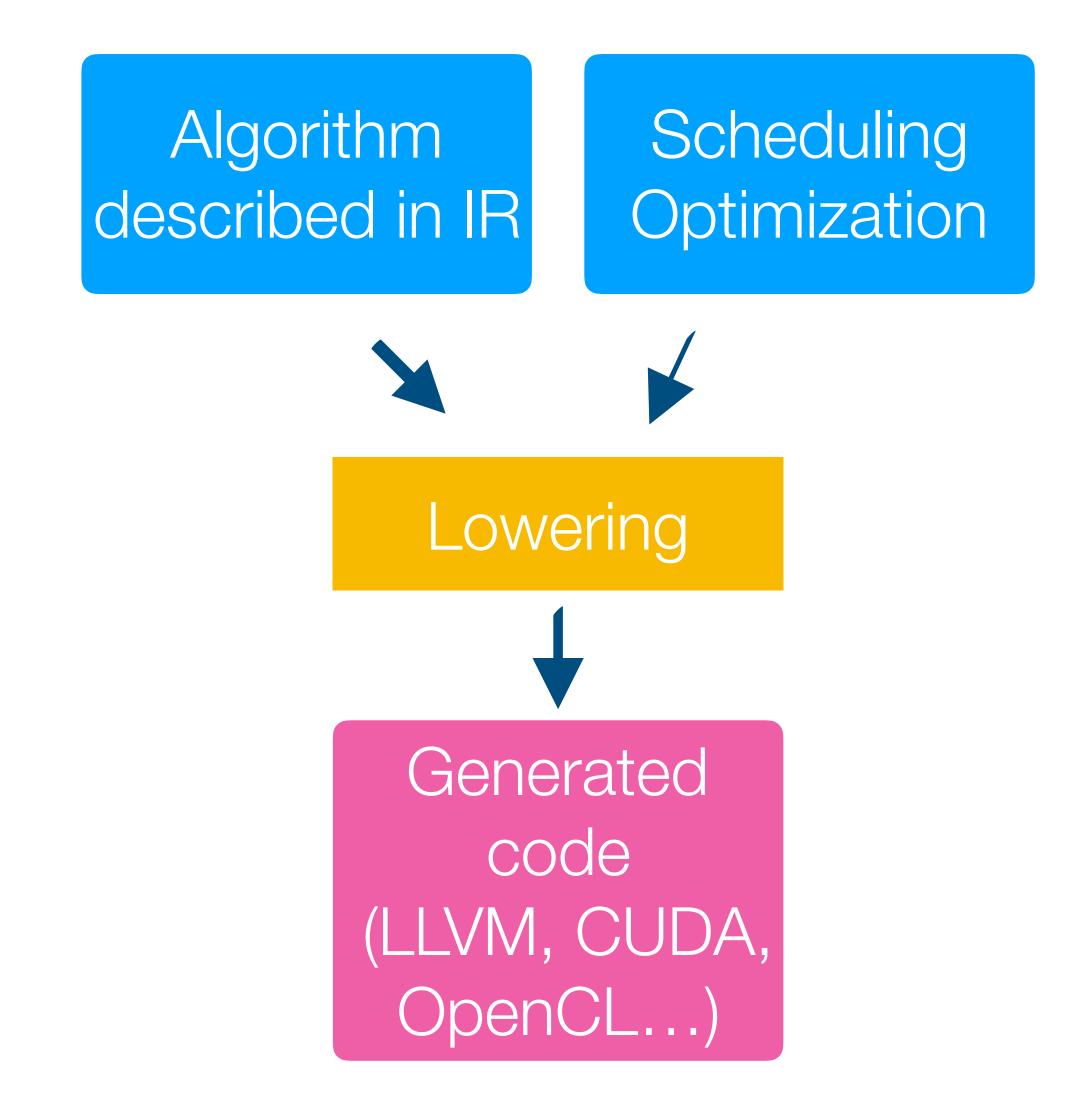

# TVM: Low Level IR

- Concise and compact description

- Explicit control on codegen

- Ease of deployment

- Support new hardware backends

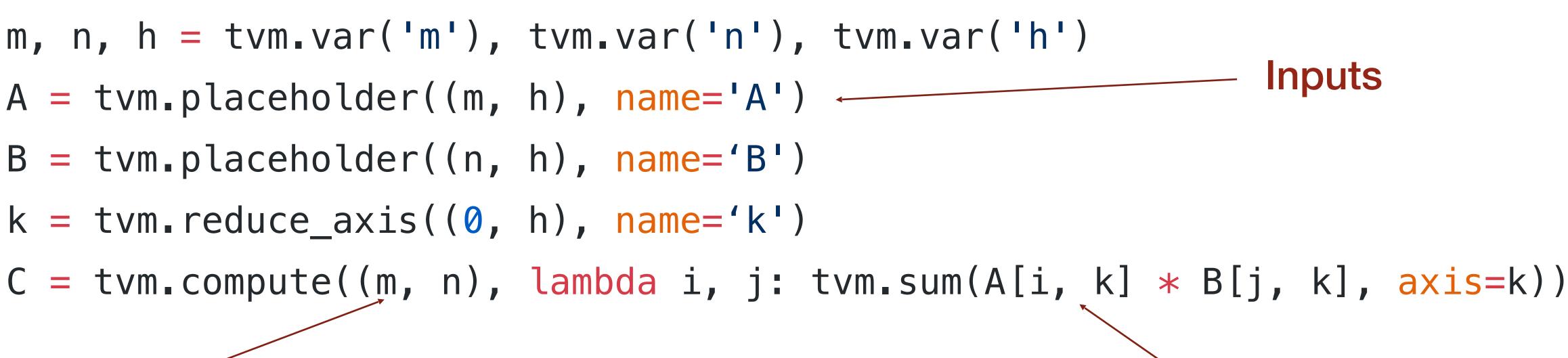

# Tensor Index Expression Declaration

### Compute C = dot(A, B.T)

import tvm

m, n, h = tvm.var('m'), tvm.var('n'), tvm.var('h')

- A = tvm.placeholder((m, h), name='A') ←

- B = tvm.placeholder((n, h), name='B')

- k = tvm.reduce\_axis((0, h), name='k')

### Shape of C

**Computation Rule**

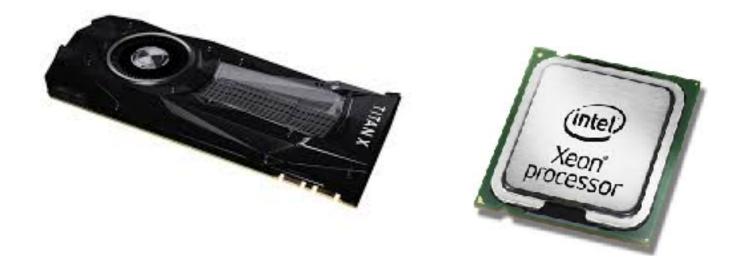

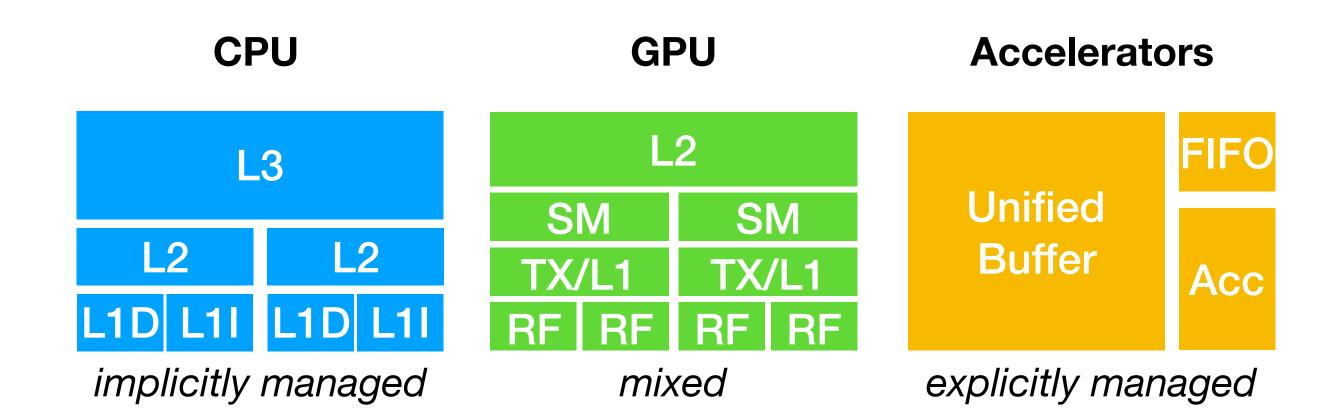

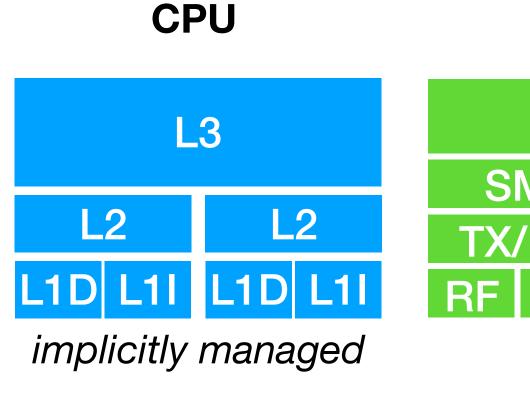

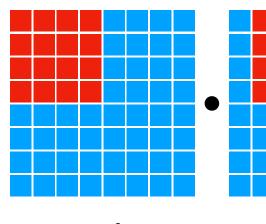

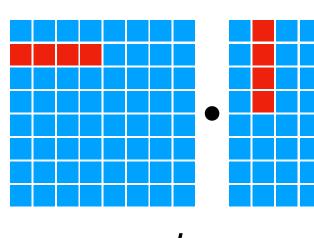

CPU

GPU

**Accelerators**

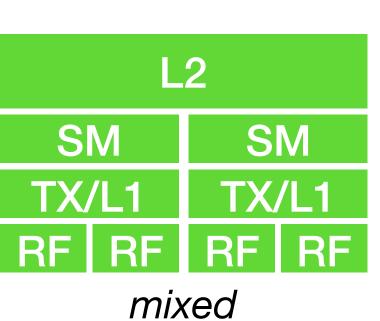

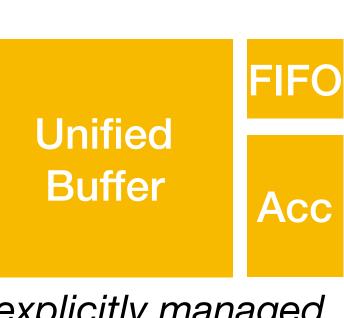

Memory subsystem

Memory subsystem

Compute primitives

GPU

**Accelerators**

scalar

vector

tensor

explicitly managed

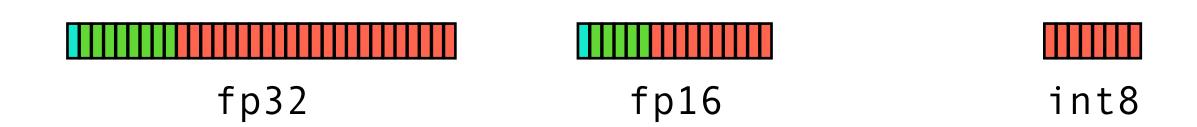

Data type

scalar

vector

tensor

## Scheduling Optimizations

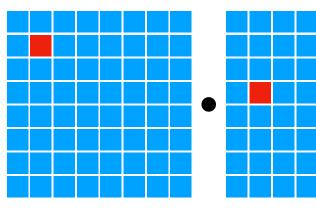

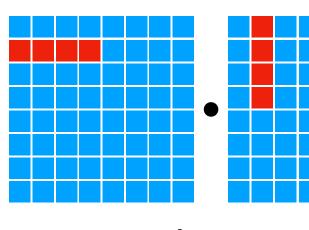

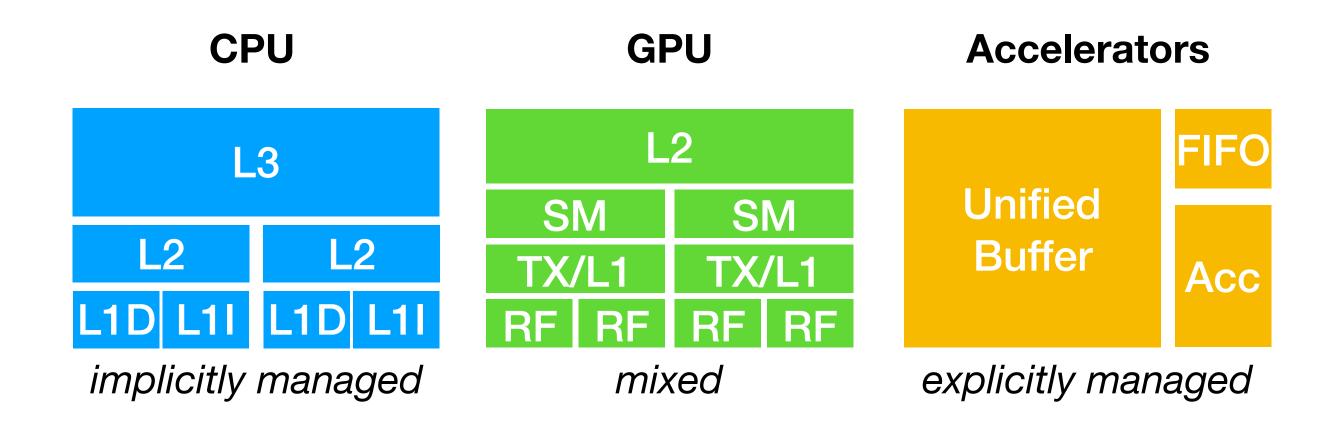

$(\checkmark)$  Data layout

## Scheduling Optimizations

$(\checkmark)$  Data layout

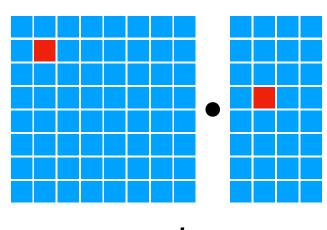

$(\checkmark)$  Tiling

## Scheduling Optimizations

- $(\checkmark)$  Data layout

- $(\checkmark)$  Tiling

- $(\checkmark)$  Thread cooperation

## Scheduling Optimizations

- $(\checkmark)$  Data layout

- $(\checkmark)$  Tiling

- $(\checkmark)$  Thread cooperation

- $(\checkmark)$  Latency hiding

## Scheduling Optimizations

- $(\checkmark)$  Data layout

- $(\checkmark)$  Tiling

- $(\checkmark)$  Thread cooperation

- $(\checkmark)$  Latency hiding

- $(\checkmark)$  Tensorization

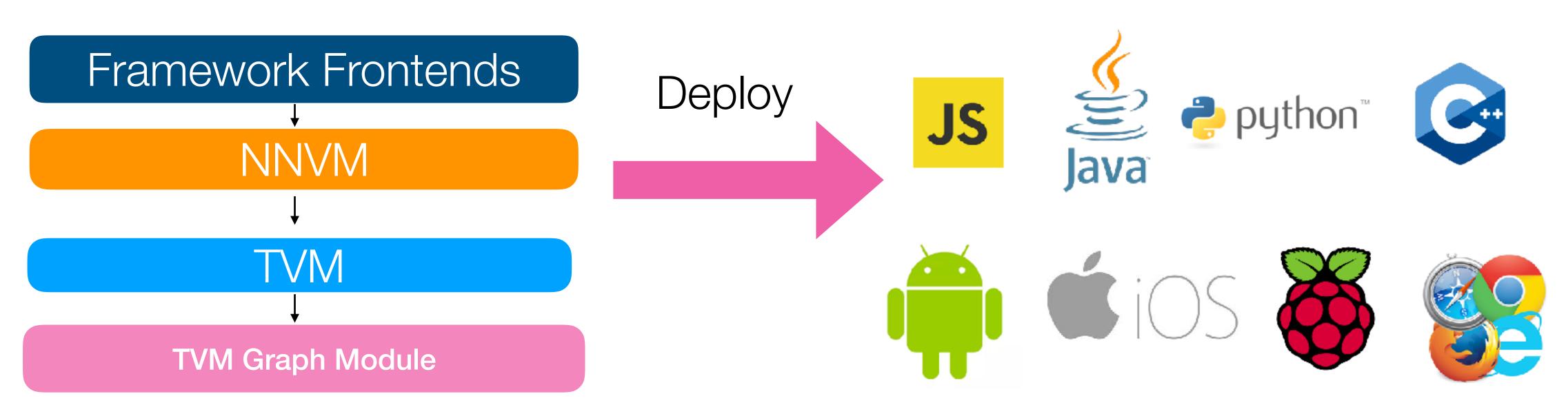

## Separation of Compilation and Deployment

Compilation Stack

### Heavy optimizations

### TVM Runtimes

### Lightweight, 300 to 600 KB

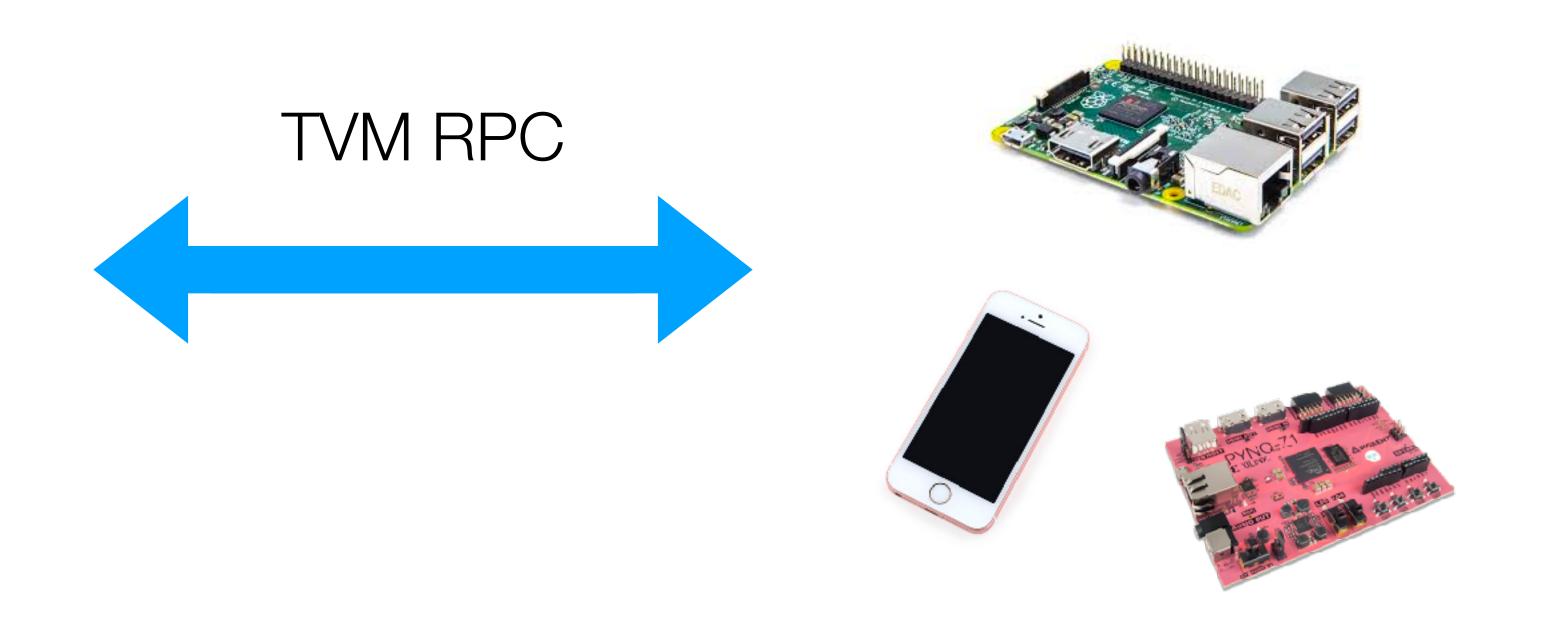

# Remote Execution and Profiling

### Server with TVM Compiler

### Devices with TVM Runtime

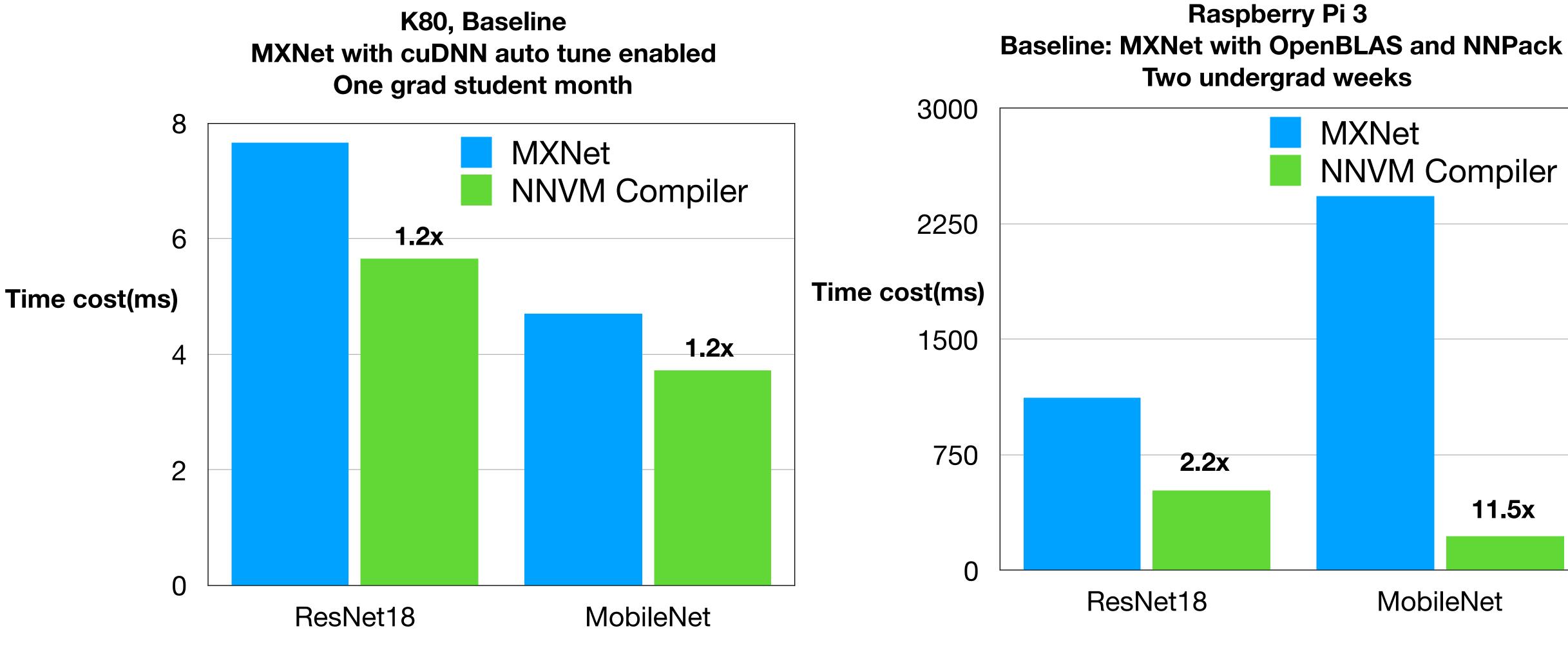

## Performance Portable against state of art

K80, Baseline One grad student month

Credit: Leyuan Wang(AWS/UCDavis), Yuwei Hu(TuSimple), Zheng Jiang(AWS/FDU)

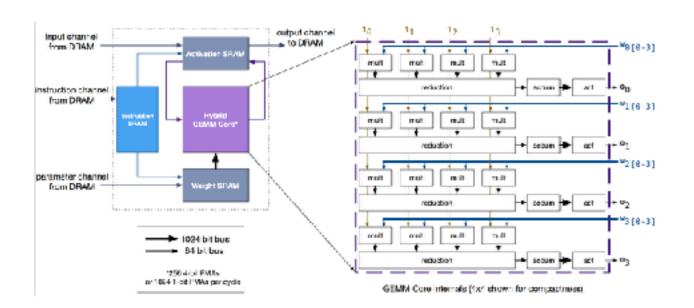

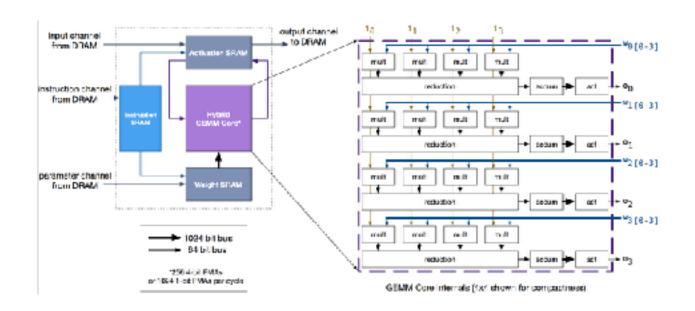

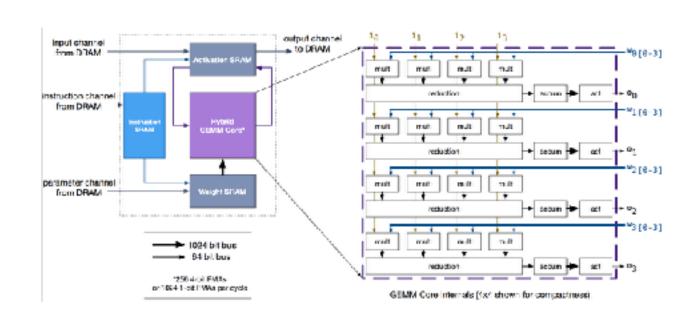

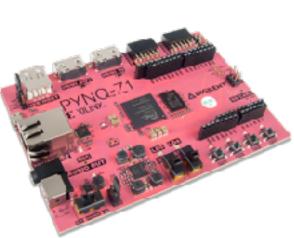

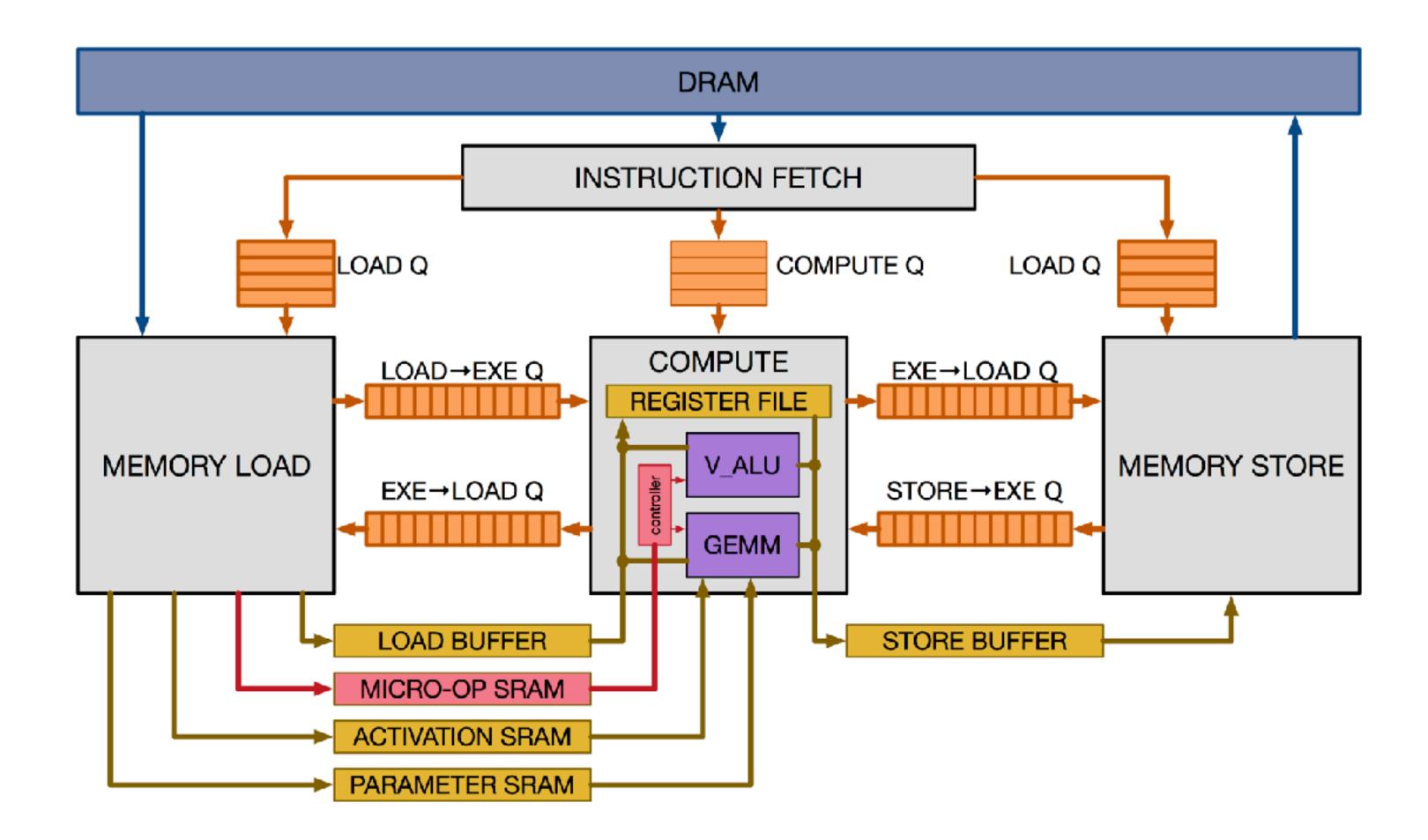

# Coming Soon: Target New Accelerators

Tensorization

Latency Hiding

FPGA Example for building new hardware backend

Open-source soon

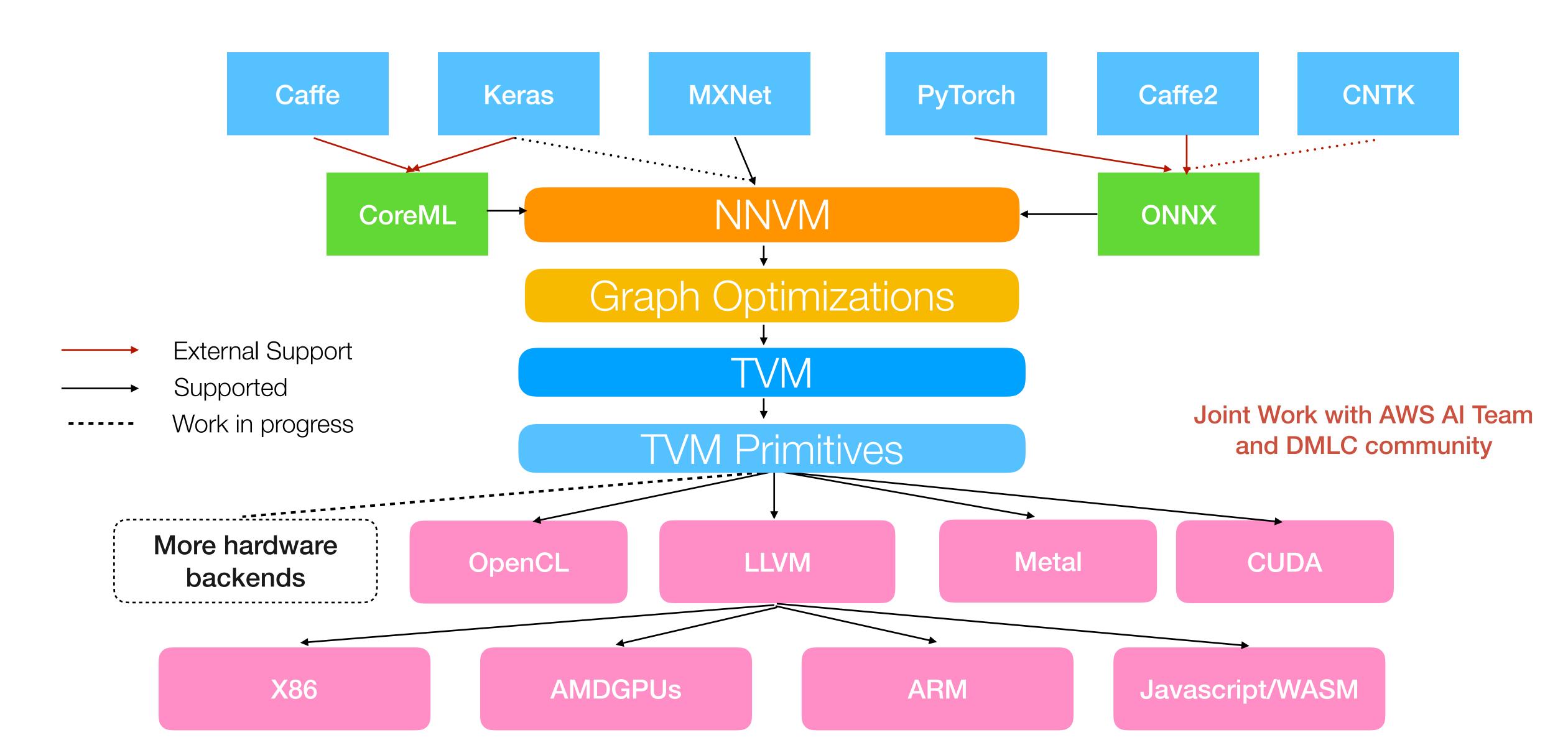

## NNVM Compiler: Open Compiler for AI Systems

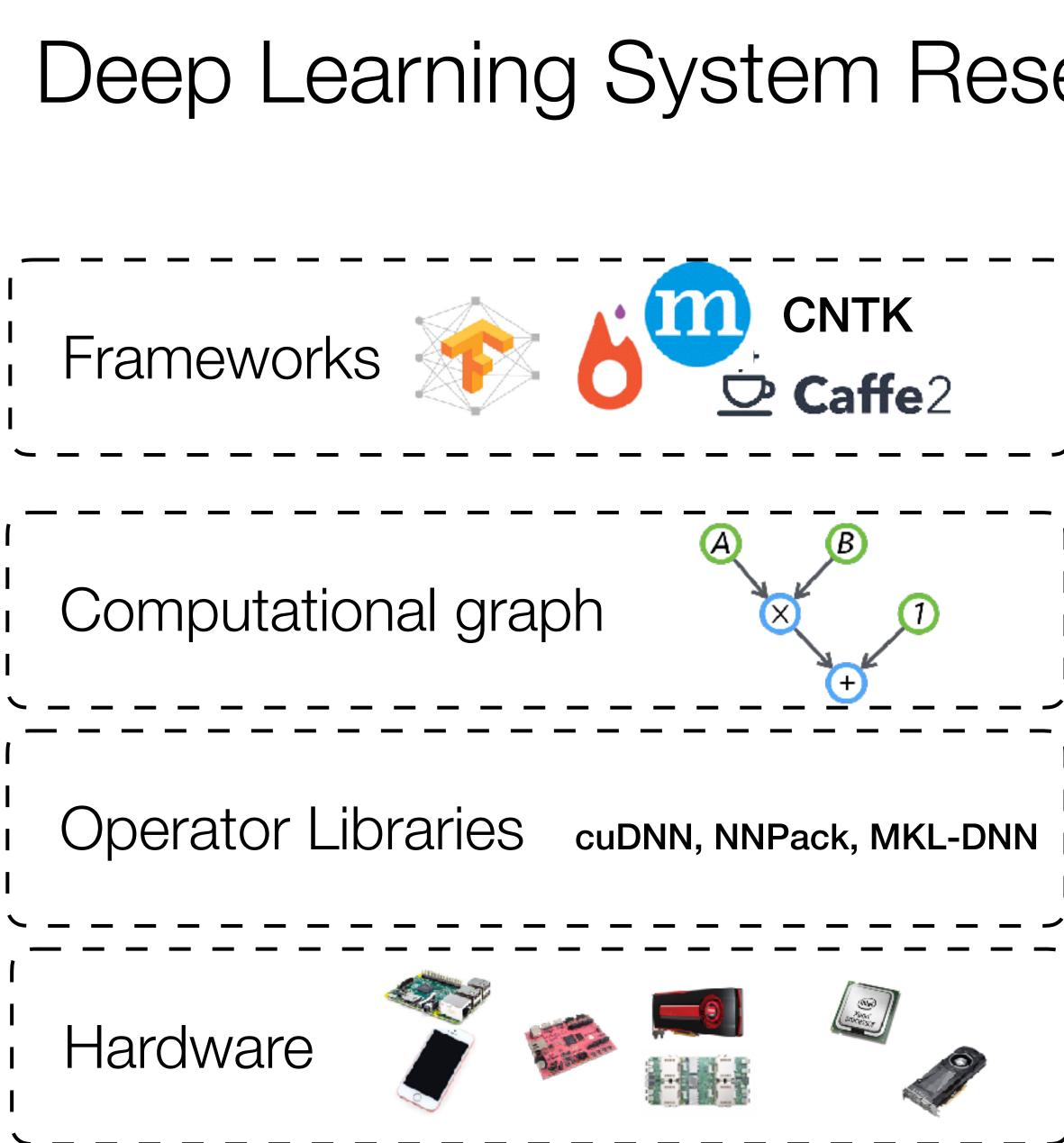

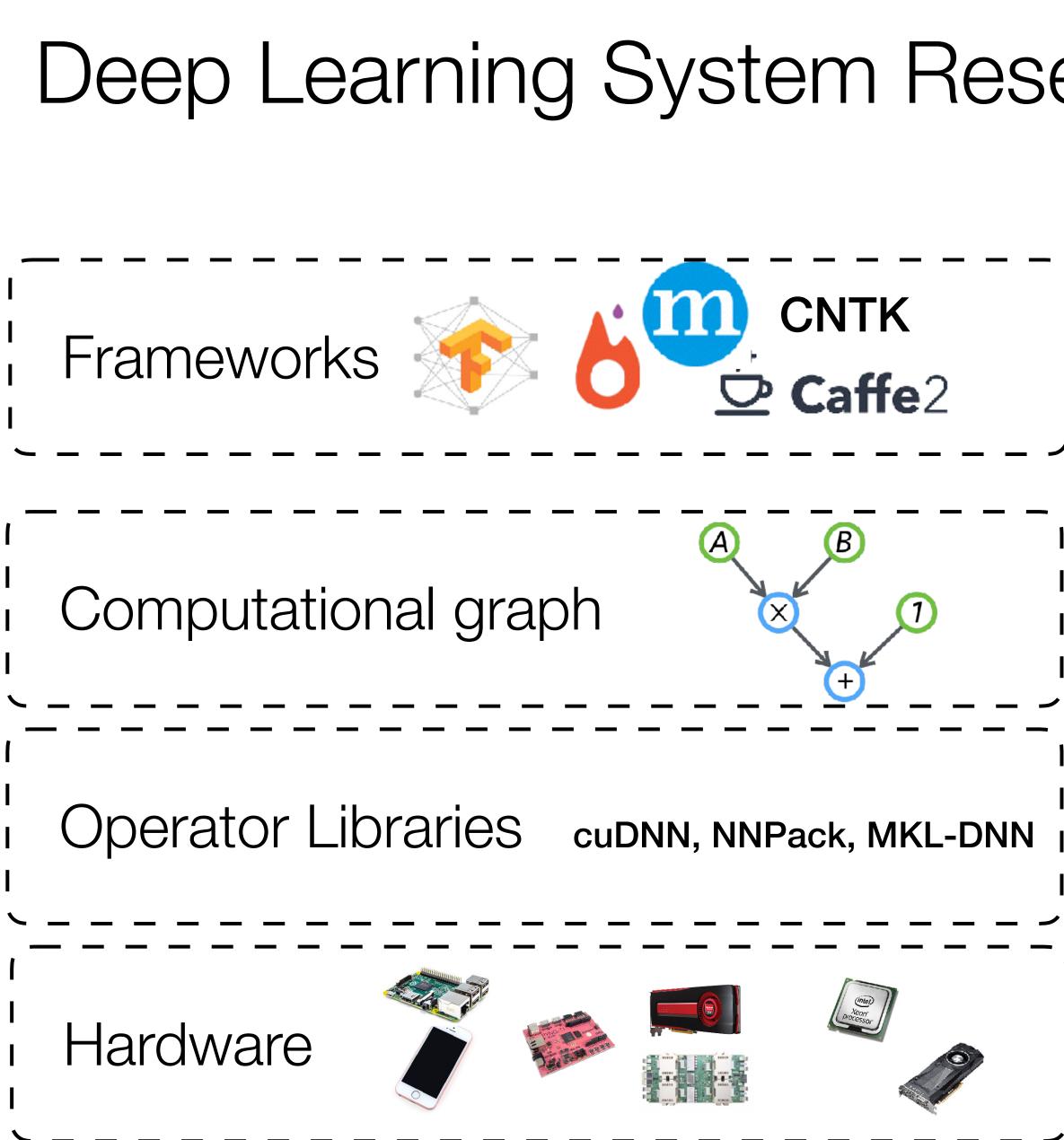

## Deep Learning System Research is Just Exciting

### **My new optimizations** works on all platforms !

### can program my new accelerators from python :)

## Deep Learning System Research is Just Exciting

# My new optimizations works on all platforms !

I can program my new accelerators from python :)

You can be part of it!